# Introduction to the STM32 L432KC MCU & Refresher on C Programming

Lecture 06

Josh Brake Harvey Mudd College

### Outline

- Introduction to the STM32-L432KC

- Review of basic architecture

- C refresher

- Common idioms to set/clear bits

- Pointers and arrays

- Structures

- Writing a simple device driver: GPIO

- Finding information in documentation

- Writing code to properly configure the peripheral

### Learning Objectives

By the end of this lecture you should be able to...

- List the basic details of the architecture of the ARM Cortex-M4 CPU used in our STM32 MCU.

- Recall basic C programming idioms and concepts (e.g., pointers, arrays, structures).

- Write a simple device driver to control the peripherals in your MCU using memorymapped I/O.

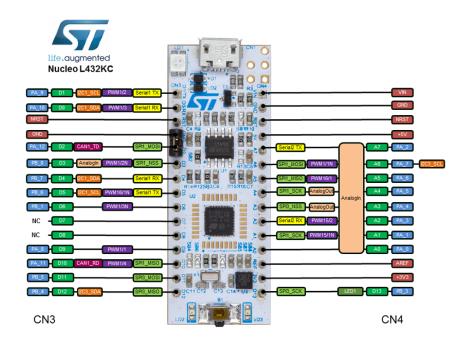

#### STM32 Nucleo-32 board

Components

- MCU STM32L432KC

- External flash memory

- 24 MHz crystal oscillator

- On-board ST-LINK debugger/programmer. Virtual COM port and debug port.

- 1 user LED and 1 reset push button

- Arduino Nano V3 form factor

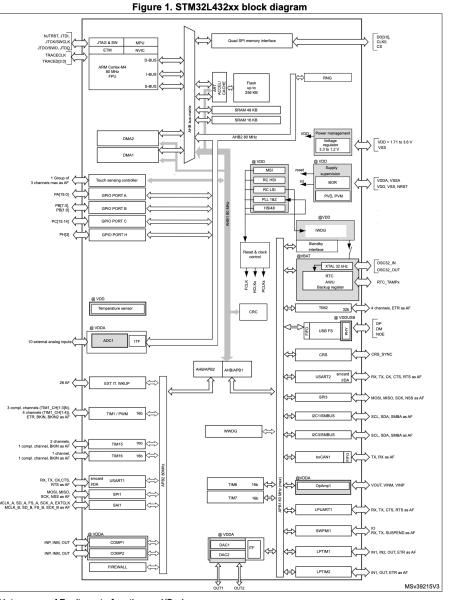

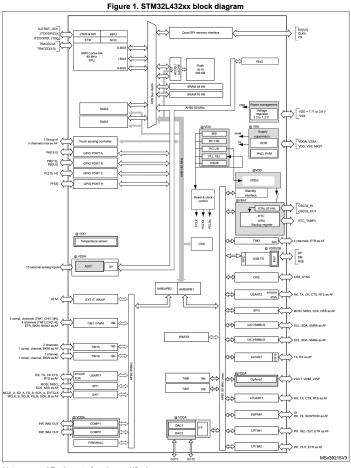

## What is an MCU

- MCU = MicroController Unit

- Processor core + peripherals

Note: AF: alternate function on I/O pins.

#### Documentation

: Information about all peripherals and their control registers

: System block diagram, Pin functions, electrical characteristics, timing

specs

: Information about the architecture (e.g., Cortex-M4),

supported assembly instructions, registers, memory map, etc.

### Questions for a new MCU

#### STM32 L432KC Architecture

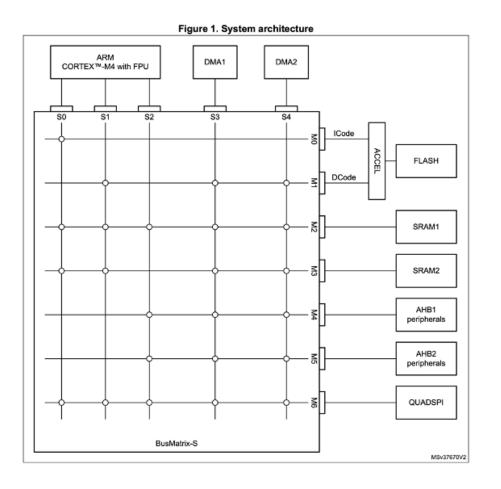

- STM32 MCU has an ARM Cortex-M4.

- It runs the ARMv7E-M architecture. This is a 32-bit architecture.

- Also supports Thumb-2 execution. Thumb-2 is a set of compressed, 16-bit instructions.

- One special thing to watch with Thumb is conditional execution. With Thumb execution you can only use conditional execution within an "if-then" block which can hold up to four successive instructions.

#### **Architecture Overview**

- Instructions are 32-bit

- Sixteen 32-bit registers R0-R15

- Supports condition codes

- Most instructions operate on two registers and put result in a third.

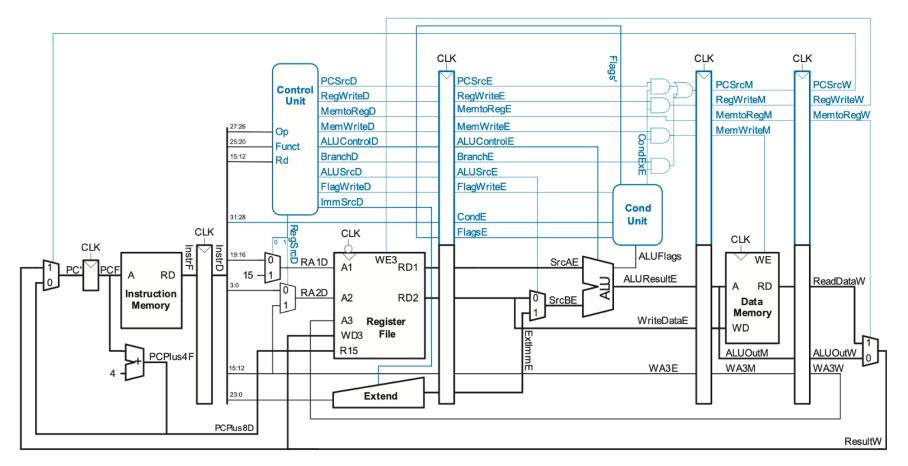

#### Microarchitecture Flashback

Figure 7.47 Pipelined processor with control

Harris and Harris, *Digital Design and Computer Architecture ARM Ed.*, p. 430

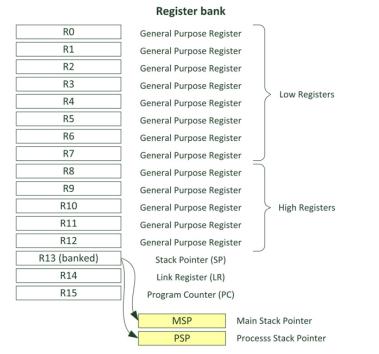

#### **Register Set**

- R15 is

- R14 is \_\_\_\_\_. Holds return addresses

- R13 by convention used as the

- Four condition codes in current program status register (CPSR)

- N -

- Z –

- C -\_\_\_\_\_

- V -

#### FIGURE 4.3

Registers in the register bank

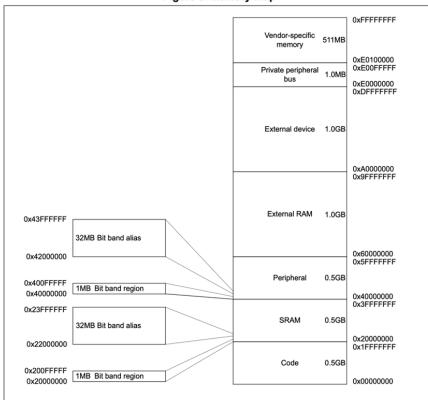

#### **Memory Map**

- Flat 32-bit instruction set

- Addressed in bytes.

- bytes of memory accessible (4 Gigabytes)

- Instructions are always aligned on word in standard ARM and halfword boundaries in

Thumb mode.

#### PM0214 Cortex-M4 Programmers Manual

## Memory Map - STM32L432KC

RM0394 p. 67

|                          |                         | Figure 2. Memory map                                    |  |

|--------------------------|-------------------------|---------------------------------------------------------|--|

| 0xFFFF FFFF              | Cortex <sup>®</sup> -M4 | 0xBFFF FFFF 0xA000 1400 Reserved                        |  |

| 7                        | with FPU<br>internal    | 0xA000 1000 QUADSPI registers                           |  |

| <u>0xE000_0000</u> _     | peripherals             | 0x5FFF FFFF 0x5006 0C00 Reserved                        |  |

| 6                        |                         | 0x4800 0000 AHB2                                        |  |

| Ũ                        |                         | 0x4002 4400 Reserved                                    |  |

| <u>0xC000</u> 0000_      |                         | AHB1                                                    |  |

| -                        | QUADSPI                 | 0x4002 0000 Reserved                                    |  |

| 5<br>0xA000 1000         | registers               | 0x4001 6400 APB2                                        |  |

| <u>0xA000_0000</u> _     |                         | 0x4001 0000 Reserved                                    |  |

|                          | QUADSPI<br>Flash bank   | 0x4000 9800                                             |  |

| 4 <sup>0x9000 0000</sup> |                         | 0x4000 0000 APB1                                        |  |

| <u>0x8000_0000</u> _     |                         | 0x1FFF FFFF                                             |  |

| 3                        |                         | Reserved                                                |  |

| 0x6000 0000              |                         | 0x1FFF 7810 Option bytes                                |  |

|                          |                         | 0x1FFF 7800 Reserved                                    |  |

| 2                        | Peripherals             | 0x1FFF 7400 OTP area                                    |  |

| 0x4000 0000              | Feripiterais            | 0x1FFF 7000 System memory                               |  |

| 1                        | SRAM2                   | 0x1FFF 0000 Reserved                                    |  |

| 1 (1)                    |                         | (2) SRAM2                                               |  |

| 0x2000_0000              | SRAM1                   | 0x1000 0000 Reserved                                    |  |

|                          | 0.1                     | 0x0808 0000 Flash memory                                |  |

| 0                        | Code                    | 0x0800 0000 Reserved                                    |  |

| 0x0000 0000              |                         | 0x0008 0000<br>Flash, system memory                     |  |

| Reserved                 |                         | or SRAM, depending<br>0x0000 0000 on BOOT configuration |  |

# **C** Programming Review

#### Important Concepts in C

- C is libertarian by nature. You can stomp on any memory address you want!

- There is no memory management built in. You must manually allocate (and deallocate!) any memory you need.

#### **Primitive Data Types in C**

| Туре           | Size (bits)       | Minimum                    | Maximum                      |

|----------------|-------------------|----------------------------|------------------------------|

| char           | 8                 | $-2^{-7} = -128$           | $2^7 - 1 = 127$              |

| unsigned char  | 8                 | 0                          | $2^8 - 1 = 255$              |

| short          | 16                | $-2^{15} = -32,768$        | $2^{15} - 1 = 32,767$        |

| unsigned short | 16                | 0                          | $2^{16} - 1 = 65,535$        |

| long           | 32                | $-2^{31} = -2,147,483,648$ | $2^{31} - 1 = 2,147,483,647$ |

| unsigned long  | 32                | 0                          | $2^{32} - 1 = 4,294,967,295$ |

| long long      | 64                | $-2^{63}$                  | $2^{63} - 1$                 |

| unsigned long  | 64                | 0                          | $2^{64} - 1$                 |

| int            | machine-dependent |                            |                              |

| unsigned int   | machine-dependent |                            |                              |

| float          | 32                | $\pm 2^{-126}$             | $\pm 2^{127}$                |

| double         | 64                | $\pm 2^{-1023}$            | $\pm 2^{1022}$               |

#### Table eC.2 Primitive data types and sizes

## Primitive Data Types in stdint.h

#### Table eC.2 Primitive data types and sizes

| Туре          | Size (bits)       | Minimum                    | Maximum                      |

|---------------|-------------------|----------------------------|------------------------------|

| char          | 8                 | $-2^{-7} = -128$           | $2^7 - 1 = 127$              |

| unsigned char | 8                 | 0                          | $2^8 - 1 = 255$              |

| int           | machine-dependent |                            |                              |

| unsigned int  | machine-dependent |                            |                              |

| int16_t       | 16                | $-2^{15} = -32,768$        | $2^{15} - 1 = 32,767$        |

| uint16_t      | 16                | 0                          | $2^{16} - 1 = 65,535$        |

| int32_t       | 32                | $-2^{31} = -2,147,483,648$ | $2^{31} - 1 = 2,147,483,647$ |

| uint32_t      | 32                | 0                          | $2^{32} - 1 = 4,294,967,295$ |

| int64_t       | 64                | $-2^{63}$                  | $2^{63} - 1$                 |

| uint64_t      | 64                | 0                          | $2^{64} - 1$                 |

| float         | 32                | $\pm 2^{-126}$             | $\pm 2^{127}$                |

| double        | 64                | $\pm 2^{-1023}$            | $\pm 2^{1022}$               |

#### **Operators and Operator Precedence**

#### Table eC.3 Operators listed by decreasing precedence

| Category       | Operator | Description                         | Example                                                  |

|----------------|----------|-------------------------------------|----------------------------------------------------------|

| Unary          | ++       | post-increment                      | a++; // a = a+1                                          |

|                |          | post-decrement                      | x; // x = x-1                                            |

|                | &        | memory address of a variable        | x = &y // x = the memory<br>// address of y              |

|                | ~        | bitwise NOT                         | Z = ~a;                                                  |

|                | !        | Boolean NOT                         | !x                                                       |

|                | -        | negation                            | y = -a;                                                  |

|                | ++       | pre-increment                       | ++a; // a = a+1                                          |

|                |          | pre-decrement                       | x; // x = x-1                                            |

|                | (type)   | casts a variable to (type)          | x = (int)c; // cast c to an<br>// int and assign it to x |

|                | sizeof() | size of a variable or type in bytes | long inty;<br>x = sizeof(y); // x = 4                    |

| Multiplicative | *        | multiplication                      | y = x * 12;                                              |

|                | /        | division                            | z = 9 / 3; // z = 3                                      |

|                | %        | modulo                              | z = 5 % 2; // z = 1                                      |

| Additive       | +        | addition                            | y = a + 2;                                               |

|                | -        | subtraction                         | y = a - 2;                                               |

| Bitwise Shift  | <<       | bitshift left                       | z = 5 << 2; // z = 0b00010100                            |

|                | >>       | bitshift right                      | x = 9 >> 3; // x = 0b00000001                            |

| Relational     | ==       | equals                              | y == 2                                                   |

|                | !=       | not equals                          | x != 7                                                   |

|                | <        | less than                           | у < 12                                                   |

|                | >        | greater than                        | val>max                                                  |

|                | <=       | less than or equal                  | z <= 2                                                   |

|                | `        |                                     |                                                          |

#### Table eC.3 Operators listed by decreasing precedence—Cont'd

| Category   | Operator | Description                        | Example                                             |

|------------|----------|------------------------------------|-----------------------------------------------------|

| Bitwise    | &        | bitwise AND                        | y = a & 15;                                         |

|            | ٨        | bitwise XOR                        | y = 2 ^ 3;                                          |

|            |          | bitwise OR                         | y = a   b;                                          |

| Logical    | & &      | Boolean AND                        | х && у                                              |

|            |          | Boolean OR                         | х    у                                              |

| Ternary    | ? :      | ternary operator                   | y = x ? a : b; // if x is TRUE,<br>// y=a, else y=b |

| Assignment | =        | assignment                         | x = 22;                                             |

|            | +=       | addition and assignment            | y += 3; // y = y + 3                                |

|            | -=       | subtraction and assignment         | z -= 10; // z = z - 10                              |

|            | *=       | multiplication and assignment      | x *= 4; // x = x * 4                                |

|            | /=       | division and assignment            | y /= 10; // y = y / 10                              |

|            | %=       | modulo and assignment              | x %= 4; // x = x % 4                                |

|            | >>=      | bitwise right-shift and assignment | x >>= 5; // x = x>>5                                |

|            | <<=      | bitwise left-shift and assignment  | x <<= 2; // x = x<<2                                |

|            | &=       | bitwise AND and assignment         | y &= 15; // y = y & 15                              |

|            | =        | bitwise OR and assignment          | x = y; // $x = x y$                                 |

|            | ^=       | bitwise XOR and assignment         | x ^= y; // x = x ^ y                                |

#### **Operator Precedence Tip!**

You should only have to remember multiplication/division before addition/subtraction. For everything else, use parentheses!

#### Important Keywords in C

- \_\_\_\_\_ prevents the compiler from using a cached value (forces load)

\_\_\_\_\_ "read-only". Prevents you from assigning a value to the variable.

- Inside a function: retains its values between calls.

- Applied to a function: visible only in this file

- •

- Applied to a function definition: has global scope (redundant)

- Applied to a variable: defined elsewhere

- As return type of function: doesn't return a value

- In a pointer declaration, the type of a generic pointer

- In a parameter list: takes no parameters

#### **Important Libraries**

- \_\_\_\_\_\_ math library: standard math functions like sin, cos, sqrt, log, exp, floor, ceil.

- \_\_\_\_\_\_ string library: functions to compare, copy, concatenate, and determine the length of a string.

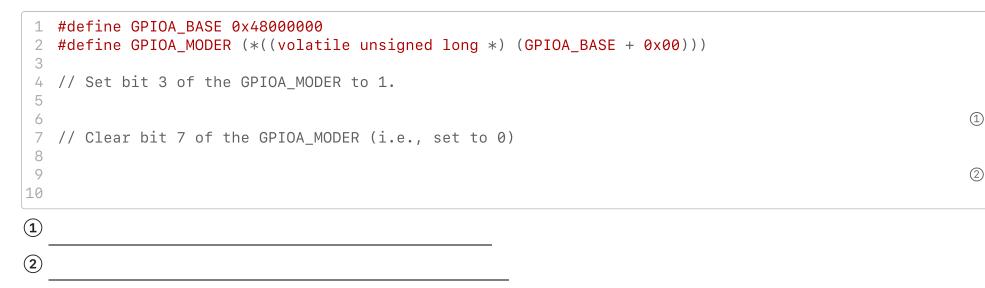

## **Setting and Clearing Bits**

#### C Idioms for Setting and Clearing Bits

## **Pointers and Arrays**

#### **Pointers and Arrays in C: Arrays**

| 1 int * p = (int*) 0x20000000; |   |

|--------------------------------|---|

| 3 int a = *p;                  | 1 |

| 5 int $b = *(p+3);$            | 2 |

| 7 *(p+5) = b;                  | 3 |

| ① Equivalent to a=             |   |

| ② Equivalent to b=, address    |   |

| ③ Equivalent to p[5]=, address |   |

#### **Pointers and Arrays in C: Strings**

```

1 char * str = (char *) 0x20001000;

2

3 str[13] = 'A';

```

1 Address

1

#### Dereferencing

```

1

2 int * p = (int*) 0x20000000;

3

4 int a = *p;

5 int * aptr = &a;

6

7 *aptr = 3;

8

9 int * ptr = &p[0];

10

11 ptr = &p[5]

12

13 *ptr = 42;

```

① Equivalent to a =

| ② aptr stores address of |   |

|--------------------------|---|

| ③ same as a=3            |   |

| <pre>④ ptr=</pre>        |   |

| <pre>⑤ ptr=</pre>        |   |

| <pre>@ p[5]=</pre>       | _ |

1

2

3

4

5

6

#### **Structures**

1 struct optional\_tag {

2 type\_1 identifier\_1;

3 type\_2 identifier\_2;

4 ...

5 type\_N identifier\_N;

6 } optional\_variable\_definitions ;

#### **Structures**

```

1 struct contact {

2     char name[30];

3     unsigned long long phone;

4     float height;

5 };

6

7 struct contact jbrake; // example variable definition

```

How many bytes does this structure occupy in memory?

## Using structures as part of a new type

Can also wrap in a typedef to avoid needing to use the struct keyword.

```

1 typedef struct my_tag {int i;} my_type; // Declaration of new type

2

3 // Creating variable with struct keyword

4

5

6

7 // Creating variable using new type

8

2

2

2

```

#### **Arrow Operator**

Use a structure to access a chunk of memory in a specific location.

```

1 typedef struct {

2    char first_name[30];

3    unsigned long long phone;

4    float height;

5 } contact_type;

6

7  contact_type jbrake;

8  strcpy(jbrake.first_name, "Josh Brake");

9  jbrake.phone = (unsigned long long) 9096218553;

10  contact_type * contact_type_ptr = &jbrake;

11  unsigned long long phone_num = contact_type_ptr->phone;

```

# Writing Device Drivers: GPIO Example

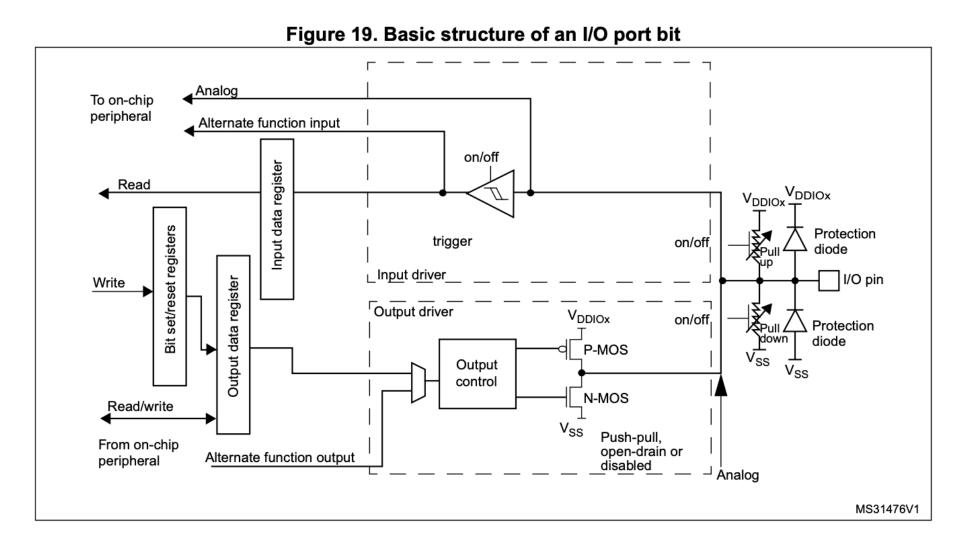

#### **GPIO Block Diagram**

### **GPIO Register Map**

| Offset | Register name                    | 31          | 30              | 29          | 28   | 27          | 26   | 25          | 24   | 23           | 22   | 21           | 20          | 19         | 18        | 17         | 16   | 15         | 14   | 13         | 12   | 11         | 10   | 6          | 8   | 7           | 9   | 5           | 4   | 3           | 2   | ۲          | •   |

|--------|----------------------------------|-------------|-----------------|-------------|------|-------------|------|-------------|------|--------------|------|--------------|-------------|------------|-----------|------------|------|------------|------|------------|------|------------|------|------------|-----|-------------|-----|-------------|-----|-------------|-----|------------|-----|

| 0x00   | GPIOA_MODER                      | MODE15[1.0] | ואיטער וטן ו.טן | MODF14[1-0] |      | MODE13[1:0] |      | MODE12[1:0] |      | MODE11[1:0]  |      | MODE10[1:0]  | [a., ]a     | MODE9[1:0] |           | MODE8[1:0] |      | MODE7[1:0] |      | MODE6[1:0] |      | MODE5[1:0] |      | MODE4[1:0] |     | MODE3[1:0]  |     | MODE2[1:0]  |     | MODF1[1:0]  |     | MODE0[1:0] |     |

|        | Reset value                      | 1           | 0               | 1           | 0    | 1           | 0    | 1           | 1    | 1            | 1    | 1            | 1           | 1          | 1         | 1          | 1    | 1          | 1    | 1          | 1    | 1          | 1    | 1          | 1   | 1           | 1   | 1           | 1   | 1           | 1   | 1          | 1   |

| 0x00   | GPIOB_MODER                      |             | ואסטר וטן ויטן. | MODF14[1:0] |      |             |      |             |      | MODE 11[1:0] |      | MODE10[1:0]  | [a]aa.a.a   | MODE911:01 | [a:.]a=aa | MODE8[1:0] |      | MODE7[1:01 |      | MODE6[1:0] |      | MODE5[1:0] |      | MODF4[1-0] |     | MODE 2[1.0] |     | MODE 211-01 |     | MODE 111-01 |     | MODE0[1:0] |     |

|        | Reset value                      | 1           | 1               | 1           | 1    | 1           | 1    | 1           | 1    | 1            | 1    | 1            | 1           | 1          | 1         | 1          | 1    | 1          | 1    | 1          | 1    | 1          | 1    | 1          | 0   | 1           | 0   | 1           | 1   | 1           | 1   | 1          | 1   |

| 0x00   | GPIOx_MODER<br>(where x = CE,H)  | MODE15[1.0] |                 | MODF14[1·0] |      | MODE13[1:0] |      |             |      | MODE11[1:0]  |      | MODE 10[1:0] | [a]a. ===== | MODE9[1:0] | [a]a= a a | MODE8[1:0] |      | MODE7[1:0] |      | MODE6[1:0] |      | MODE5[1:0] |      | MODF4[1-0] |     | MODE3[1:0]  |     | MODE2[1:0]  |     | MODE1[1:0]  |     | MODE0[1:0] |     |

|        | Reset value                      | 1           | 1               | 1           | 1    | 1           | 1    | 1           | 1    | 1            | 1    | 1            | 1           | 1          | 1         | 1          | 1    | 1          | 1    | 1          | 1    | 1          | 1    | 1          | 1   | 1           | 1   | 1           | 1   | 1           | 1   | 1          | 1   |

| 0x04   | GPIOx_OTYPER<br>(where x = AE,H) | Res.        | Res.            | Res.        | Res. | Res.        | Res. | Res.        | Res. | Res.         | Res. | Res.         | Res.        | Res.       | Res.      | Res.       | Res. | 0T15       | 0T14 | OT13       | 0T12 | OT11       | OT10 | 0Т9        | OT8 | 017         | ОТб | 015         | 0T4 | ОТ3         | 0Т2 | 0Т1        | 0Т0 |

|        | Reset value                      |             |                 |             |      |             |      |             |      |              |      |              |             |            |           |            |      | 0          | 0    | 0          | 0    | 0          | 0    | 0          | 0   | 0           | 0   | 0           | 0   | 0           | 0   | 0          | 0   |

Table 37. GPIO register map and reset values

RM0394 p. 274

### Steps for writing a device driver for a new peripheral

#### 1. Look at block diagram

- 2. Note what elements in the diagram need to be configured

- 3. Find relevant registers and bits

- 4. Write code

- 1. Base address for peripheral

- 2. Create structure to define registers

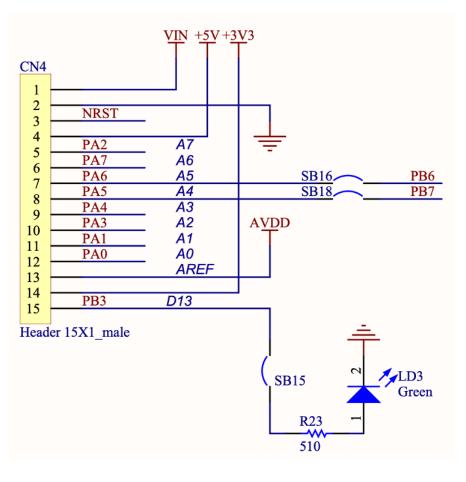

#### **Blink LED**

On-board LED connected to pin PB3.

UM1956 p. 33

#### Enabling peripheral clock

#### 6.2.18 Peripheral clock enable register (RCC\_AHBxENR, RCC\_APBxENRy)

Each peripheral clock can be enabled by the xxxxEN bit of the RCC\_AHBxENR, RCC\_APBxENRy registers.

When the peripheral clock is not active, the peripheral registers read or write accesses are not supported.

The enable bit has a synchronization mechanism to create a glitch free clock for the peripheral. After the enable bit is set, there is a 2 clock cycles delay before the clock be active.

**Caution:** Just after enabling the clock for a peripheral, software must wait for a delay before accessing the peripheral registers.

RM0394 p. 191

Note: AF: alternate function on I/O pins.

DS11451 p. 13

#### Finding clock enable bit for GPIOB

#### 6.4.16 AHB2 peripheral clock enable register (RCC\_AHB2ENR)

Address offset: 0x4C

Reset value: 0x0000 0000

Access: no wait state, word, half-word and byte access

Note: When the peripheral clock is not active, the peripheral registers read or write access is not supported.

| 31   | 30   | 29    | 28   | 27   | 26   | 25        | 24   | 23               | 22       | 21        | 20               | 19               | 18               | 17               | 16               |

|------|------|-------|------|------|------|-----------|------|------------------|----------|-----------|------------------|------------------|------------------|------------------|------------------|

| Res. | Res. | Res.  | Res. | Res. | Res. | Res.      | Res. | Res.             | Res.     | Res.      | Res.             | Res.             | RNG<br>EN        | res.             | AESEN<br>(1)     |

|      |      |       |      |      |      |           |      |                  |          |           |                  |                  | rw               |                  | rw               |

| 15   | 14   | 10    | 40   | 44   | 40   | 0         | 0    | 7                | •        | -         |                  | •                | •                |                  |                  |

|      | 14   | 13    | 12   | 11   | 10   | 9         | 8    | /                | 6        | 5         | 4                | 3                | 2                | 1                | 0                |

| Res. | res. | ADCEN | res. | Res. | Res. | 9<br>Res. | res. | 7<br>GPIOH<br>EN | formers. | o<br>res. | 4<br>GPIOE<br>EN | 3<br>GPIOD<br>EN | 2<br>GPIOC<br>EN | 1<br>GPIOB<br>EN | 0<br>GPIOA<br>EN |

1. Available on STM32L42xxx, STM32L44xxx and STM32L46xxx devices only.

RM0394 p. 218

#### Where is that bit located?

1. Look in system and memory overview section

2. Look RCC register mapping to find register and bit offsets

|      |                  |      |      |        |      |      |      |           |      |         |      |      |       |                      |           |                  |                |       |        |         |         |      | 0.      |         |         |           | • • • • • |        |       | 1.0001104          |                                                   |

|------|------------------|------|------|--------|------|------|------|-----------|------|---------|------|------|-------|----------------------|-----------|------------------|----------------|-------|--------|---------|---------|------|---------|---------|---------|-----------|-----------|--------|-------|--------------------|---------------------------------------------------|

|      |                  |      |      |        |      |      |      |           |      |         |      |      |       |                      |           |                  |                |       |        |         |         |      | 0x4     | 002     | 2 400   | 0 - 0     | 0x4002    | 2 43FF | 1 KB  | TSC                | Section 23.6.11: TSC register map                 |

|      |                  |      |      |        |      |      |      |           |      |         |      |      |       |                      |           |                  |                |       |        |         |         |      | 0x4     | 002     | 2 340   | 0 - 0     | 0x4002    | 2 3FFF | 1 KB  | Reserved           | -                                                 |

|      |                  |      |      |        |      |      |      |           |      |         |      |      |       |                      |           |                  |                |       |        |         |         |      | 0x4     | 002     | 2 300   | 0 - 0     | 0x4002    | 2 33FF | 1 KB  | CRC                | Section 14.4.6: CRC register map                  |

|      |                  |      |      |        |      |      |      |           |      |         |      |      |       |                      |           |                  |                |       |        |         |         |      | 0x4     | 002     | 2 240   | 0 - 0     | 0x4002    | 2 2FFF | 3 KB  | Reserved           | -                                                 |

|      |                  |      |      |        |      |      |      |           |      |         |      |      |       |                      |           |                  |                |       |        |         |         |      | 0x4     | 002     | 2 200   | 0 - 0     | 0x4002    | 2 23FF | 1 KB  | FLASH<br>registers | Section 3.7.13: FLASH register map                |

|      |                  |      |      |        |      |      |      |           |      |         |      |      |       |                      |           |                  |                |       |        |         | AH      | B1   | 0x4     | 002     | 2 140   | 0 - 0     | 0x4002    | 2 1FFF | 3 KB  | Reserved           | -                                                 |

|      |                  |      |      |        |      |      |      |           |      |         |      |      |       |                      |           |                  |                |       |        |         |         |      | 0x4     | 002     | 2 100   | 0 - 0     | 0x4002    | 2 13FF | 1 KB  | RCC                | Section 6.4.32: RCC register map                  |

|      |                  |      |      |        |      |      |      |           |      |         |      |      |       |                      |           |                  |                |       |        |         |         |      | 0x4     | 002     | 2 080   | 0 - 0     | 0x4002    | 2 0FFF | 2 KB  | Reserved           | -                                                 |

|      |                  |      | +    | +      | +    | +    | +    | ßT        |      | +       | _    | +    |       |                      |           | SI               | ╞              |       | 0      |         |         | +    |         | +       | +       | ßT        | 4002      | 2 07FF | 1 KB  | DMA2               | Section 11.6.8: DMA register map and reset values |

| 0x40 | RCC_<br>APB2RSTR | Res. | Res. | Res.   | Res. | Res. | Res. | DFSDM1RST | Res. | CALADET |      | Res. | Res.  | TIM16RST<br>TIM15RST | Res.      | USART1RST<br>Res | <b>SPI1RST</b> | IM1RS | Res.   | Res.    | Res.    | Res. | Res.    | Res.    | Res.    | SYSCFGRST | 4002      | 2 03FF | 1 KB  | DMA1               | Section 11.6.8: DMA register map and reset values |

|      |                  |      |      |        |      |      |      | Ц         |      | 0       | 0    |      |       | F                    |           | S                | S              | μ     | ק      |         |         |      |         |         |         |           | 100       |        | 30 KB | Record             | _                                                 |

|      | Reset value      |      |      |        |      |      |      | 0         |      | (       | 2    |      |       | 0 0                  |           | 0                | 0              | 0     | 2      |         |         |      |         |         |         | 0         |           |        |       |                    |                                                   |

| 0x48 | RCC_AHB1<br>ENR  | Res. | Res. | Res.   | Res. | Res. | Res. | Res.      | Res. | Res.    | Res. | Res. | Res.  | TSCEN.               | Res.      | Res.             | CRCEN          | Res.  | Res.   | FLASHEN | Res.    | Res. | Res.    | Res.    | DMA2EN  | DMA1EN    |           |        |       |                    |                                                   |

|      | Reset value      |      | 1    | $\top$ |      |      |      |           |      |         |      | 1    |       | 0                    | $\square$ |                  | 0              |       | $\top$ | 1       |         |      |         |         | 0       | 0         |           |        |       |                    |                                                   |

| 0x4C | RCC_AHB2<br>ENR  | Res. | Res. | Res.   | Res. | Res. | Res. | Res.      | Res. | Res.    | Res  | Res. | RNGEN | AESEN                | Res.      | ADCFN            |                | Res.  | Res.   | Res.    | GPIOHEN | Res. | GPIOEEN | GPIODEN | GPIOBEN | GPIOAEN   |           |        |       |                    |                                                   |

|      | Reset value      |      |      |        |      |      |      |           |      |         |      |      | 0     | 0                    |           | 0                |                |       |        |         | 0       |      | 0       | 0 0     | 0 0     | 0         |           |        |       |                    |                                                   |

### Configuration steps to enable basic GPIO: RCC

Turn on clock domain in Reset and Clock Control (RCC)

\_\_\_\_\_

**RCC** base address:

RCC\_AHB2ENR register offset:

Bit for GPIOB\_EN:

### Configure pin as output in GPIO register block

Configure pin as an output (GPIO\_MODER)

Base address of GPIOB:

Offset of MODER register:

Bits in MODER to be set:

Value for relevant bits to configure pin as output:

#### **Blink Demo: Includes**

```

1 // Nucleo-L432KC Blink demo

2 // Josh Brake

3 // jbrake@hmc.edu

4 // 9/21/22

5 #include <stdint.h>

6 #define GPIOB_BASE_ADR (0x48000400UL)

7 #define RCC_BASE_ADR (0x40021000UL)

8 #define RCC_AHB2ENR ((uint32_t *) (RCC_BASE_ADR + 0x4C))

9 #define GPIOB_MODER ((uint32_t *) (GPIOB_BASE_ADR + 0x00))

10 #define GPIOB_ODR ((uint32_t *) (GPIOB_BASE_ADR + 0x14))

11 #define DUMMY_DELAY 100000

12

13 ...

```

#### Blink Demo: main

```

1 ...

2

3 int main(void) {

4   // Initialization code

5   *RCC_AHB2ENR |= (1 << 1);

6   // Set PB3 as output (MODER bit 7 to 0 and bit 6 to 1)

7   *GPIOB_MODER &= ~(1 << 7);

8   *GPIOB_MODER |= (1 << 6);

9  while(1) {

10   for(volatile int i = 0; i < DUMMY_DELAY; i++);

11   *GPIOB_ODR ^= (1 << 3);

12 }</pre>

```

## **Miscellanous Notes**

#### Using MCU while connected to development board

- Make sure that you have the MCU\_+5V header connected. This ensures the on-board voltage regulators work which makes sure the reset signal is held high. If not, you won't be able to connect to your MCU to program it (the reset pin will float and the MCU will always be in reset!)

- Remove jumper that came installed by default on the Nucleo board (connects reset to ground!)

#### Using structures to model memory-mapped I/O

|    | // Base addresses for GPIO ports<br>#define GPIOA_BASE (0x48000000U)                     |

|----|------------------------------------------------------------------------------------------|

| 3  | typedef struct                                                                           |

| 4  | {                                                                                        |

| 5  | IO uint32_t MODER; /*!< GPIO port mode register, Address offset: 0x00 */                 |

| 6  | IO uint32_t OTYPER; /*!< GPIO port output type register, Address offset: 0x04 */         |

| 7  | IO uint32_t OSPEEDR; /*!< GPIO port output speed register, Address offset: 0x08 */       |

| 8  | IO uint32_t PUPDR;  /*!< GPIO port pull-up/pull-down register, Address offset: 0x0C */   |

| 9  | IO uint32_t IDR; /*!< GPIO port input data register, Address offset: 0x10 */             |

|    | IO uint32_t ODR; /*!< GPIO port output data register, Address offset: 0x14 */            |

|    | IO uint32_t BSRR;  /*!< GPIO port bit set/reset register, Address offset: 0x18 */        |

|    | IO uint32_t LCKR; /*!< GPIO port configuration lock register, Address offset: 0x1C */    |

|    | IO uint32_t AFR[2]; /*!< GPIO alternate function registers, Address offset: 0x20-0x24 */ |

| 14 | IO uint32_t BRR; /*!< GPIO Bit Reset register, Address offset: 0x28 */                   |

| 15 | } GPIO_TypeDef;                                                                          |

\_\_\_IO is defined with a #define statement to one of the C keywords we discussed earlier. Which one?

#### Wrap Up

- C is libertarian will allow you to do many things, not all of which are good for you.

- Understanding certain C data structures like pointers and structures will enable you to more easily and naturally write code to control your MCU.

- The MCU reference manual contains the information needed to write code to configure and manipulate the peripherals using memory-mapped I/O.