# Alien Voice Filter

Final Project Report

December 1, 2020

E155

# Dithi Ganjam and Rebecca Qin

### **ABSTRACT**

The goal of this project was to build a voice filter that would allow users to record a snippet of their voice and play it back with three filters: one that increases the frequency of the voice, one that decreases the speed of the voice, and one that modifies the frequency to make it sound like an "alien" voice. The user interface for the voice filter is an online webpage. Our device consists of a microphone, a microcontroller, a DAC, a speaker, and a WiFi module. The user's voice input into the microphone is sampled and stored in the microcontroller. The audio is then modified and outputted to the DAC according to the user's request. The output of the DAC is then amplified and then sent to the speaker.

#### I. INTRODUCTION

Audio filters are entertaining features that are used all over social media nowadays. We can see their functionality in apps like Snapchat, TikTok, etc. The motivation for this project was to apply our knowledge of STM32F401RE functionality to recreate a voice-filtering web page of our own. We sought out to design a webpage that allows the user to record their voice and play the audio clip back with four main options: regular playback (no filter), slow playback, sped-up playback, and an alien voice using amplitude modulation [1].

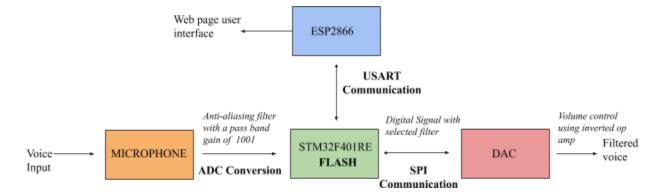

This project entails reading voice input from a microphone into memory on the microcontroller using the ADC feature of the STM32F401RE, processing the audio input based on user input implemented via an IoT interface, and outputting the modified audio signal to a speaker to play it back. The block diagram in Figure 1 below outlines the general flow of the system and the communication between the microcontroller and the various peripherals.

Figure 1. Top-level block diagram of our voice filter, which includes the STM32 interfacing with various peripherals.

#### II. NEW HARDWARE

The project contains only one new piece of hardware, which is the CMA-4544PF-W microphone. The microphone takes in an audio signal and outputs a voltage signal that can be fed into the ADC to store the user's voice data. While the microphone itself was the only new piece of hardware implemented, it required extensive signal processing circuitry to generate an intelligible voice signal from the microphone output. Before the output of the microphone was sent into the ADC, it was first passed through an anti-aliasing filter with a cutoff frequency of 20 kHz (to capture the frequency range of voice) and to avoid aliasing in accordance with the Shannon-Nyquist sampling theorem, as we sample at a rate of 40 kHz. It was then passed through a differential amplifier to reduce the offset voltage and ensure that the integrity of the signal was not compromised (or clipped on the top). The set-up of the input to the ADC, including the details of the anti-aliasing filter and its circuitry, can be found in Section III. Once the voice signal is sent into the ADC, it is converted into a digital signal and stored into memory.

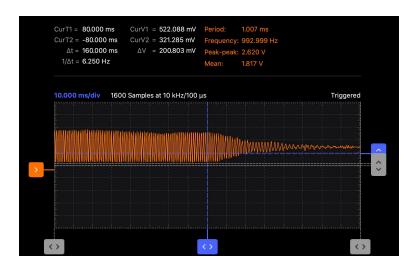

Figure 2. Example of microphone output of a scream (post analog processing)

#### III. SCHEMATICS

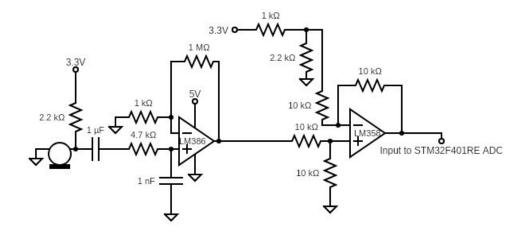

Figure 3. Butterworth Low Pass Filter (with cutoff Frequency 40kHz) and Differential

Amplifier circuit for amplification and offset (to avoid signal clipping)

The circuit in figure 3 demonstrates the analog filtration circuitry that was necessary to convert the microphone output signal into an intelligible digital voice signal that could be stored and recreated. The output of the microphone first passed through a low pass butterworth filter with a cutoff frequency of 40kHz, and a band pass gain of 1001. The original voltage swing of the microphone output was on the order of a few millivolts, so the band pass gain allowed for the oscillation in the voice signal to be amplified to the extent that it could be accurately captured and preserved as a voltage level (or digital signal). However, in order to ensure that the voltage swing was large enough, the gain factor led to the signal being positively offset relative to ground. Due to the large gain factor coupled with the offset, the signal was beginning to be clipped on the top by the maximum read voltage of the ADC which is 3.6V. Therefore, the signal is also filtered using a differential amplifier, which brings down the offset of the amplified signal

so that even with a 2 to 3V voltage swing, the input signal is not clipped by the maximum voltage of ADC input.

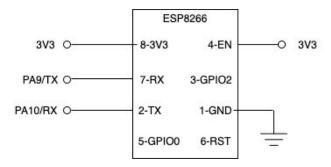

Figure 4. ESP8266 Circuit configuration for Serving the webpage

Figure 4 shows the schematic of the physical interface between the ESP8266 Wifi module and the STM32F401RE microcontroller. The transmit pin, or TX, of the microcontroller goes to the receive pin, or RX, of the ESP chip and vice versa enabling USART communication. The chip enable is tied to 3.3V so that the wifi module knows to be able to receive and send data to the microcontroller.

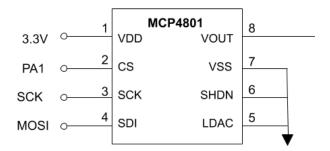

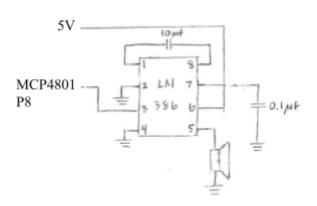

Figure 5. MCP4801 Circuit configuration between the DAC and the STM32F401RE

The figure above shows the interface between the digital to analog converter (DAC) and the microcontroller. The input to SCK on the DAC is controlled by a timer in order to output the signal at the appropriate frequency so the integrity of the signal is maintained. The chip select is

controlled by GPIOA pin 1, and the discrete voltage signal is sent to the MCP4801 from the MOSI of the microcontroller to the serial data input of the DAC. The voltage swing of the output of the DAC is approximately 2V, while for most 8 Ohm speakers, a reasonably loud audio output is around 8V. For this reason, the analog output of the MCP480, from pin 8, is fed through to the audio amplification circuit outlined in figure 6 below.

Figure 6. Audio Amplification circuit using LM386

Lastly, a simple green LED was wired to GPIOA 8 and grounded to inform the user of when the microcontroller was recording, and when it had stopped.

#### IV. MICROCONTROLLER DESIGN

The microcontroller design for handling the audio input is as follows. The audio input from the microphone is retrieved using the built-in ADC in single-conversion mode. A timer controls the sampling of the audio so that when the timer generates an interrupt, the ADC is turned on and captures one data point of the audio signal. The flash memory of the microcontroller is used to store the audio data. Specifically, sectors 6 and 7 are used in order to avoid writing data to sectors that might be used for code [2]. Each of the two sectors used are 128 kbytes, resulting in a total of 256 kbytes, and a storage capacity of about 130,000 audio data points, where each point is a 12-bit positive integer. We originally planned on using the DMA to transfer data from the ADC data register to the flash memory, but after looking further into this, we found that using DMA would not improve the efficiency of the data transfer and might even decrease the efficiency, so we decided against implementing this feature.

Next, we outline the microcontroller design for outputting the audio. The SPI is initialized to send the 12-bit data from the microcontroller to the DAC. Another timer is initialized in a similar way as the sampling timer to output the audio data at the correct frequency. The auto-reload register value for the timer initialized changes according to the audio filter selected. For the alien filter, a function manipulates the audio data point dynamically, as it is being outputted through the SPI. For the other playback options, the data point is unmodified as it is sent through the SPI.

Finally, we outline the microcontroller design for rendering the webpage for the user interface. Two USARTs are initialized: one for communicating with the ESP8266 WiFi module, and one for sending the data received from the ESP8266 to the serial monitor. To initialize the ESP, the proper AT commands are sent using the ESP USART. Then, the webpage is rendered

by sending the HTML through the ESP USART when there is a request through the ESP's IP address. The serial monitor USART is used to check that the ESP is functioning and responding to the commands.

#### V. RESULTS

The completed project was partially successful. Due to unforeseen issues with the computer that the microcontroller was programmed with, the hardware malfunctioned. The device was thus unable to gather an audio input from the microphone. Before the hardware malfunction, each of the individual components of the high-level design was working separately (1) the webpage controlling the recording and playback functionality, though not yet in flash memory, and (2) writing to flash memory, and being able to apply the different voice filters, though not yet controlled by the IoT interface. Before we could interface our two implementations, unfortunately our hardware failed. However, we were successfully able to design and implement our four voice filters. We were able to meet most of the requirements outlined in our project proposal, but since essential hardware for our system broke, we are unable to demonstrate a working voice filter.

The main challenge that we faced was with using the ESP8266 WiFi module along with the flash memory. In the beginning, we attempted to use sectors 1-7 of flash memory. Upon implementing this and running the code on the microcontroller, we discovered that the ESP had stopped being functional. This may have been from our program in the flash memory being overwritten by the audio values. Although we did not determine the reason for the ESP's loss of function, once we reprogrammed our code to use only sectors 6 and 7, a replacement ESP was able to function correctly.

There is much room for improvement in our project design. Due to the lack of resources from remote learning, we lost much time from needing to order small parts that needed to be replaced. One stretch goal that we would have liked to implement is an additional autotuning filter, which would require looking into fast Fourier transforms (FFTs) to modify the audio data.

#### VI. REFLECTION

Though we could not complete our project due to unforeseen hardware issues, working through the project both together and remotely was an important learning experience. Overall, we were not prepared in advance for our hardware to fail at any point (resulting in not having extra components). In future projects, similar outcomes may be avoided by ordering extra components in the event that anything goes wrong. Another example of such a hurdle is that our only 1 out of 5 ESP8266 Wifi modules was functioning appropriately. Initially, when the ESP8266 chips were not functioning as expected, we experimented with an external power supply for increased reliability, and a variety of baud rates. However, later upon plugging it into the logic analyzer on the SCOPY digital oscilloscope, we realized that the ESP was not communicating in response to the microcontroller, as we could only see bits communicated from the TX pin of the microcontroller, and none received on the RX pin. However, for the 5th ESP8266 that we tried, we were able to observe communication between the ESP and the microcontroller, and also serve the webpage for our IoT interface. While the project itself was incomplete as new hardware could not be ordered in time before the final due date, working through our software issues allowed us to better understand the inner workings of flash memory on STM32F401RE microcontroller. Though we encountered issues along the way, the project taught us the importance of debugging and understanding how different components interact with one another (for example, how the ESP8266 stores information in certain flash sectors). It was also a lesson learned on the volatility and fragility of electrical components. While we could not pinpoint exactly what caused our hardware to fail, we suspect it occured when the computer we were working on began to glitch and eventually crashed, also impacting the monitor and mouse, after which our hardware also began to fail.

# VII. REFERENCES

- Bezzam, Eric. "3.1 How It Works." DSP Labs, 2018, lcav.gitbook.io/dsp-labs/alien-voice/effect\_description.

- Biswal, Sanskar. "Programming FLASH ROM in STM32." Medium,

TheTeamMavericks, 25 May 2020,

medium.com/theteammavericks/programming-flash-rom-in-stm32-f5b7d6dcba4f.

## VIII. PARTS LIST

The table below lists the parts that were used for this project.

| Part                              | Sources           | Vendor Part # | Price  |

|-----------------------------------|-------------------|---------------|--------|

| CMA-4544PF-W<br>Microphone        | Digi-Key          | 102-1721-ND   | \$0.77 |

| LM386 Audio<br>Amplifier          | Texas Instruments | 4/NOPB        | \$1.17 |

| AS358P                            | Spark Fun         | 945JB2        | \$0.95 |

| ESP8266 WiFi<br>Module            | Spark Fun         | WRL-13678     | \$6.95 |

| Speaker 0.5W 8 ohm                | Adafruit          | 1891          | \$1.75 |

| Breadboard Power<br>Supply Module | Inland            | 078584        | \$3.99 |

#### IX. APPENDIX

#### Microcontroller Code

```

#include "STM32F401RE.h"

#include "main.h"

#include <string.h>

#include <math.h>

#include "UARTRingBuffer.h"

int count = 0; // count up to 248,000 for full FLASH memory (sector 1-7)

size t NUM SAMPLES = 130000; // sector 6-7

int recording = 0;

int play index = 0;

uint16 t *FLASH SECTOR 6 ADDRESS = (uint16 t *) 0x08040000;

int TYPE = NORMAL;

const uint16 t arr for sampling = 2100;

void initADCTIM(void) {

TIM2 -> EGR \mid = 1;

TIM2->ARR = arr for sampling;

TIM2->DIER |= 0b1; // TIM DIER UIE

NVIC EnableIRQ(TIM2 IRQn);

TIM2 -> CR1 |= 1;

void initPlayTIM(uint16 t arr) {

```

```

TIM4->EGR \mid = 1;

TIM4->ARR = arr;

NVIC EnableIRQ(TIM4 IRQn);

TIM4 -> CR1 |= 1;

void initESP8266(USART TypeDef * ESP USART, USART TypeDef * TERM USART) {

uint8 t volatile str[BUFFER SIZE] = "";

sendString(ESP USART, "ATE1\r\n");

delay millis(DELAY TIM, CMD DELAY MS);

readString(ESP USART, str);

delay millis(DELAY TIM, CMD DELAY MS);

sendString(TERM USART, str);

delay millis(DELAY TIM, CMD DELAY MS);

sendString(ESP USART, "AT+CWMODE=3\r\n");

delay millis(DELAY TIM, CMD DELAY MS);

readString(ESP USART, str);

delay millis(DELAY TIM, CMD DELAY MS);

sendString(TERM USART, str);

delay millis(DELAY TIM, CMD DELAY MS);

sendString(ESP USART, "AT+CIPMUX=1\r\n");

delay millis(DELAY TIM, CMD DELAY MS);

readString(ESP USART, str);

delay millis(DELAY TIM, CMD DELAY MS);

sendString(TERM USART, str);

delay millis(DELAY TIM, CMD DELAY MS);

sendString(ESP USART, "AT+CIPSERVER=1,80\r\n");

delay millis(DELAY TIM, CMD DELAY MS);

```

```

readString(ESP USART, str);

delay millis(DELAY TIM, CMD DELAY MS);

sendString(TERM USART, str);

delay millis(DELAY TIM, CMD DELAY MS);

uint8 t connect cmd[128] = "";

sprintf(connect cmd,"AT+CWJAP=\"%s\",\"%s\"\r\n", SSID, PASSWORD);

sendString(ESP USART, connect cmd);

delay millis(DELAY TIM, CMD DELAY MS);

readString(ESP USART, str);

delay millis (DELAY TIM, CMD DELAY MS);

sendString(TERM USART, str);

delay millis (DELAY TIM, CMD DELAY MS);

delay millis(DELAY TIM, 30000);

sendString(ESP USART, "AT+CIFSR\r\n");

delay millis(DELAY TIM, CMD DELAY MS);

readString(ESP USART, str);

delay millis (DELAY TIM, CMD DELAY MS);

sendString(TERM USART, str);

void serveWebpage(uint8 t str []) {

uint8_t cmd response[BUFFER SIZE] = "";

uint32 t str length = strlen(str)+2;

```

```

memset(cmd response, 0, BUFFER SIZE);

sendString(TERM USART, "Serving: ");

sendString(TERM USART, str);

sendString(TERM USART, "\r\n");

memset(cmd response, 0, BUFFER SIZE);

sprintf(cmd, "AT+CIPSEND=0,%d\r\n",str length);

sendString(ESP USART, cmd);

delay millis(DELAY TIM, CMD DELAY MS);

readString(ESP USART, cmd response);

sendString(TERM USART, cmd response);

memset(cmd response, 0, BUFFER SIZE);

sendString(ESP USART, str);

sendString(ESP USART, "\r\n");

delay millis(DELAY TIM, CMD DELAY MS);

readString(ESP USART, cmd response);

sendString(TERM USART, cmd response);

void play(int type, int arr) {

TYPE = type;

initPlayTIM(arr);

void TIM4 IRQHandler(void) {

TIM4->SR &= \sim (0b1);

if (play index == NUM SAMPLES) play index = 0; //TIM4->CR1 &= ~(0b1);

uint16 t note = *(FLASH SECTOR 6 ADDRESS + play index);

if (TYPE == ALIEN) {

note = (uint16 t) ((double) (note * (((double)

sin(2*3.14*(900/40000)*play index)+1))));

```

```

spiSendReceive12(note);

void EXTI15 10 IRQHandler(void) {

if (EXTI->PR & (1 << BUTTON PIN)) {

EXTI->PR \mid = (1 << BUTTON PIN);

if (recording) {

TIM2->CR1 &= \sim (0b1); // disable timer

ADC1->CR2.ADON = 0; // turn off ADC

digitalWrite(GPIOA, LED PIN, GPIO LOW);

recording = 0;

initFLASH(); // RAM

count = 0;

initADCTIM();

digitalWrite(GPIOA, LED PIN, GPIO HIGH);

recording = 1;

void TIM2 IRQHandler(void) {

TIM2->SR &= \sim (0b1);

if (count < NUM SAMPLES) {//VOLTAGE ARRAY SIZE) { // RAM</pre>

configureADC();

```

```

TIM2->CR1 &= \sim (0b1); // disable timer

ADC1->CR2.ADON = 0; // turn off ADC

digitalWrite(GPIOA, LED PIN, GPIO LOW);

recording = 0;

void ADC IRQHandler(void) {

*(FLASH SECTOR 6 ADDRESS + count) = (uint16 t) ADC1->DR.DR;

while(FLASH->SR.BSY == 1);

++count;

void USART1 IRQHandler() {

int main(void) {

configureFlash();

configureClock();

RCC->AHB1ENR.GPIOAEN = 1;

RCC->AHB1ENR.GPIOCEN = 1;

RCC->APB2ENR.ADC1EN = 1;

RCC->APB2ENR.SYSCFGEN = 1;

RCC->APB2ENR.SPI1EN = 1;

```

```

RCC->APB1ENR.TIM2EN = 1;

RCC->APB1ENR.TIM3EN = 1;

RCC->APB1ENR.TIM4EN = 1;

RCC->APB1ENR.TIM5EN = 1;

initDelayTIM(DELAY TIM);

initDelayTIM(TIM3);

pinMode (GPIOA, LED PIN, GPIO OUTPUT);

pinMode(GPIOC, BUTTON PIN, GPIO INPUT); // button press

pinMode(GPIOA, GPIO PAO, GPIO ANALOG); // ADC pin

enable irq();

*SYSCFG EXTICR4 |= 0b00100000; // Set EXTICR4 for PC13 to 2

EXTI->IMR |= 1 << 13; // PC13 is EXTI13

EXTI->RTSR &= ~(1 << 13); // PC13 is EXTI13

EXTI->FTSR |= 1 << 13; // PC13 is EXTI13

NVIC EnableIRQ(EXTI15 10 IRQn); // enable button interrupt

NVIC EnableIRQ(ADC IRQn); // enable ADC interrupt

USART TypeDef * ESP USART = initUSART(ESP USART ID, 115200);

USART TypeDef * TERM USART = initUSART (TERM USART ID, 115200);

*NVIC ISER1 |= (1 << 5);

ESP USART->CR1.RXNEIE = 1;

init ring buffer();

flush buffer();

```

```

delay millis(DELAY TIM, 1000);

initESP8266(ESP USART, TERM USART);

delay millis(DELAY TIM, 500);

uint8 t volatile http request[BUFFER SIZE] = "";

uint8 t volatile temp str[BUFFER SIZE] = "";

while(1) {

memset(http request, 0, BUFFER SIZE);

volatile uint32 t http req len = 0;

if(is data available()) {

memset(temp str, 0, BUFFER SIZE);

readString(ESP USART, temp str); // Read in available

strcat(http_request, temp str); // Append to current

http req len = strlen(http request); // Store length of

delay millis(DELAY TIM, 20); // Delay

} while(is data available()); // Check for end of transaction

sendString(TERM USART, http request);

volatile uint8 t get request = look for substring("GET",

http request);

if(get request == 1){

volatile uint8 t button req = look for substring("REQ",

http request);

volatile uint8 t favicon req =

look for substring("favicon", http request);

```

```

if(!favicon req){

if(button req == 1){

volatile uint8 t button req type;

if(look for substring("=PLAY", http request))

button req type = REQ PLAY;

else if(look for substring("=SLOW", http request))

button req type = REQ SLOW;

else if(look for substring("=FAST", http request))

button req type = REQ FAST;

else if(look for substring("=ALIEN",

http request)) button req type = REQ ALIEN;

switch(button req type){

play(NORMAL, normal);

sendString(TERM USART, "Playing back

regular voice.\n");

play(NORMAL, slow);

sendString(TERM USART, "Playing voice

slowed down.\n");

play(NORMAL, fast);

sendString(TERM USART, "Playing voice sped

up.\n");

play(ALIEN, normal);

```

```

sendString(TERM USART, "Playing alien

voice.\n");

sendString(TERM USART, "Unknown

request.\n");

serveWebpage("<!DOCTYPE html>");

serveWebpage("<meta name=\"viewport\"</pre>

content=\"width=device-width, initial-scale=1.0\">");

serveWebpage("<title>Alien Voice Filter</title>");

serveWebpage("<h3 style=\"color:Green;\">~~ALiEn vOicE

FiLteR~~</h3>");

serveWebpage("<p</pre>

style=\"color:RebeccaPurple;\">Welcome to the spooky alien voice

filter!");

serveWebpage("Press the

blue button on the microcontroller to start recording your voice. Press

the button again to stop. The recording will automatically stop after a

set amount of time.");

serveWebpage("<p</pre>

style=\"color:MediumSlateBlue;\">After you record, press one of the

buttons below to play your filtered voice back.");

serveWebpage("<form action=\"REQ=PLAY\"</pre>

style=\"background-color:SpringGreen;\"><input type=\"submit\" value =

\"Playback\"></form>");

serveWebpage("<form action=\"REQ=SLOW\"</pre>

style=\"background-color:Indigo;\"><input type=\"submit\" value = \"Slow

Down\"></form>");

serveWebpage("<form action=\"REQ=FAST\"</pre>

style=\"background-color:LimeGreen;\"><input type=\"submit\" value =

\"Speed Up\"></form>");

serveWebpage("<form action=\"REQ=ALIEN\"</pre>

style=\"background-color:DarkViolet;\"><input type=\"submit\" value =

\"Alien Voice\"></form>");

```

```

// Close connection

memset(temp_str, 0, BUFFER_SIZE);

sendString(ESP_USART, "AT+CIPCLOSE=0\r\n");

readString(ESP_USART, temp_str);

sendString(TERM_USART, temp_str);

}

```

```

files

#ifndef MAIN H

#define MAIN H

#include "STM32F401RE.h"

#define NORMAL 0

#define ALIEN 1

#define fast 0

#define slow 1

#define normal 2

```

```

#define SSID "Fios-QS9zf"

#define PASSWORD "yes753code39jab"

#define NVIC ISERO ((uint32 t *) 0xE000E100UL)

#define NVIC_ISER1 ((uint32 t *) 0xE000E104UL)

#define SYSCFG EXTICR4 ((uint32 t *) (0x40013800UL + 0x14UL))

typedef struct {

volatile uint32 t IMR;

volatile uint32 t EMR;

volatile uint32 t FTSR;

volatile uint32 t SWIER;

volatile uint32 t PR;

}EXTI TypeDef;

#define EXTI ((EXTI TypeDef *) 0x40013C00UL)

#define NSS PIN GPIO PA1

#define SPI1CLK PIN GPIO PA5

#define MISO PIN GPIO PA6

#define MOSI PIN GPIO PA7

#define BUTTON PIN 13 // PC13

#define LED PIN GPIO PA8

// Request defines

#define REQ UNKNOWN 0

#define REQ PLAY 1

#define REQ SLOW 2

#define REQ FAST 3

#define REQ ALIEN 4

#define ESP USART ID USART1 ID

#define TERM USART ID USART2 ID

#define ADC TIM TIM2

#define PLAY TIM TIM4

#define DELAY TIM TIM5

#define CMD DELAY MS 100

#define BUFFER SIZE 2048

```

```

typedef enum

Interrupt

Interrupt

Interrupt

Interrupt

Interrupt

Interrupt

detection Interrupt

interrupts through the EXTI line

```

```

the EXTI line

EXTI3 IRQn

EXTI4 IRQn

Interrupt

Interrupt

Interrupt

DMA1 Stream3 IRQn = 14, /*! < DMA1 Stream 3 global

Interrupt

Interrupt

Interrupt

Interrupt

Interrupts

global interrupt

TIM10 global interrupt

Interrupt and TIM11 global interrupt */

```

```

Interrupt

= 34, /*! < I2C2 Error Interrupt

= 36, /*!< SPI2 global Interrupt

= 38, /*!< USART2 global Interrupt

Interrupts

= 41,

EXTI Line Interrupt

= 42,

EXTI line interrupt

= 47,

= 49, /*!< SDIO global Interrupt

```

```

/*!< DMA2 Stream 1 global

Interrupt

Interrupt

DMA2 Stream3 IRQn = 59,

Interrupt

Interrupt

interrupt

interrupt

interrupt

= 84 /*!< SPI4 global Interrupt

IRQn Type;

#define NVIC PRIO BITS

the Priority Levels */

#include "cmsis gcc.h"

#include "core cm4.h"

#endif // MAIN H

```

```

#include "STM32F401RE FLASH.h"

void configureFlash() {

FLASH->ACR.LATENCY = 2; // Set to 0 waitstates

FLASH->ACR.PRFTEN = 1; // Turn on the ART

void clearFlash() {

while(FLASH->SR.BSY== 1);

FLASH->CR.SNB = 0b0110;

FLASH->CR.SER = 1;

FLASH->CR.STRT = 1;

while (FLASH->SR.BSY== 1);

FLASH->CR.SNB = 0b0111;

FLASH->CR.SER = 1;

FLASH->CR.STRT = 1;

while(FLASH->SR.BSY== 1);

void initFLASH() {

FLASH->KEYR = 0x45670123;

FLASH->KEYR = 0xCDEF89AB; // enable write to CR

FLASH->OPTKEYR = 0 \times 08192A3B;

FLASH->OPTKEYR = 0x4C5D6E7F; // enable write to OPTCR

FLASH->CR.PSIZE = 0b01; // half-word (16-bits)

FLASH->OPTCR.RDP = 0xaa;

FLASH->OPTCR.nWRP = 0b111111110;

FLASH->OPTCR.SPRMOD = 0;

clearFlash();

FLASH->CR.PG = 1;

#ifndef STM32F4 FLASH H

```

```

#define STM32F4 FLASH H

#include <stdint.h>

#define IO volatile

#define FLASH BASE (0x40023C00UL) // base address of RCC

typedef struct {

IO uint32 t PRFTEN :1;

IO uint32 t

:19;

IO uint32 t PGSERR :1;

```

```

IO uint32 t RDERR :1;

:1;

:4;

:1;

:6;

:1;

:5;

IO uint32 t OPTSTRT :1;

:8;

typedef struct {

```

```

offset: 0x04 */

offset: 0x08 */

Address offset: 0x0C */

Address offset: 0x10 */

IO FLASH OPTCR bits OPTCR; /*! < FLASH option control register ,

Address offset: 0x14 */

IO uint32 t OPTCR1; /*! < FLASH option control register 1, Address

offset: 0x18 */

FLASH TypeDef;

#define FLASH ((FLASH TypeDef *) FLASH BASE)

void configureFlash();

void clearFlash();

void initFLASH();

#endif

// STM32F401RE TIM.c

#include "STM32F401RE TIM.h"

#include "STM32F401RE RCC.h"

void initDelayTIM(TIM TypeDef * TIMx){

uint32 t psc div = (uint32 t) ((SystemCoreClock/1e6)-1);

```

```

TIMx -> PSC = (psc div - 1);

TIMx \rightarrow EGR \mid = 1;

TIMx \rightarrow CR1 \mid = 1; // Set CEN = 1

void delay millis(TIM TypeDef * TIMx, uint32 t ms){

TIMx->ARR = ms*1000;// Set timer max count

TIMx->EGR |= 1; // Force update

TIMx->SR &= \sim (0x1); // Clear UIF

TIMx - > CNT = 0; // Reset count

void delay micros(TIM TypeDef * TIMx, uint32 t us){

TIMx->ARR = us; // Set timer max count

TIMx->EGR |= 1; // Force update

TIMx->SR &= \sim (0x1); // Clear UIF

TIMx -> CNT = 0; // Reset count

while(!(TIMx->SR & 1)); // Wait for UIF to go high

```

```

#define IO volatile

#define PERIPH BASE

0 \times 40000000 L /*! < Peripheral base address in

the alias region

#define APB1PERIPH BASE

#define APB2PERIPH BASE

#define TIM1 BASE

(APB2PERIPH BASE + 0x0000UL)

#define TIM2 BASE

(APB1PERIPH BASE + 0x0000UL)

#define TIM3 BASE

(APB1PERIPH BASE + 0x0400UL)

#define TIM4 BASE

(APB1PERIPH BASE + 0x0800UL)

#define TIM5 BASE

(APB1PERIPH BASE + 0x0C00UL)

#define TIM9 BASE

#define TIM10 BASE

#define TIM11 BASE

typedef struct

Address offset: 0x00 */

Address offset: 0x04 */

IO uint32 t SMCR;

Address offset: 0x08 */

Address offset: 0x0C */

Address offset: 0x10 */

Address offset: 0x14 */

```

```

IO uint32 t CCMR1;

Address offset: 0x18 */

Address offset: 0x1C */

Address offset: 0x20 */

IO uint32 t CNT;

Address offset: 0x24 */

IO uint32 t PSC;

Address offset: 0x28 */

Address offset: 0x2C */

Address offset: 0x30 */

IO uint32 t CCR1;

Address offset: 0x34 */

Address offset: 0x38 */

IO uint32 t CCR3;

Address offset: 0x3C */

Address offset: 0x40 */

IO uint32 t BDTR;

Address offset: 0x44 */

IO uint32 t DCR;

Address offset: 0x48 */

IO uint32 t DMAR;

Address offset: 0x4C */

Address offset: 0x50 */

} TIM TypeDef;

#define TIM1 ((TIM TypeDef *) TIM1 BASE)

#define TIM2 ((TIM TypeDef *) TIM2 BASE)

#define TIM3 ((TIM TypeDef *) TIM3 BASE)

#define TIM4 ((TIM TypeDef *) TIM4 BASE)

#define TIM5 ((TIM TypeDef *) TIM5 BASE)

#define TIM9 ((TIM TypeDef *) TIM9 BASE)

#define TIM10 ((TIM TypeDef *) TIM10 BASE)

```

```

#define TIM11 ((TIM TypeDef *) TIM11 BASE)

void initDelayTIM(TIM TypeDef * TIMx);

void delay millis(TIM TypeDef * TIMx, uint32_t ms);

void delay micros(TIM TypeDef * TIMx, uint32 t us);

#endif

#include "STM32F401RE RCC.h"

void configurePLL() {

RCC->CR.PLLON = 0; // Turn off PLL

while (RCC->CR.PLLRDY != 0); // Wait till PLL is unlocked (e.g., off)

RCC->PLLCFGR.PLLSRC = PLLSRC HSE;

RCC->PLLCFGR.PLLM = 8;

RCC->PLLCFGR.PLLN = 336;

RCC->PLLCFGR.PLLP = 0b01; // divide by 4

RCC->PLLCFGR.PLLQ = 4;

RCC->CR.PLLON = 1;

```

```

void configureClock(){

RCC->CFGR.PPRE2 = 0b000;

RCC->CFGR.PPRE1 = 0b100;

RCC->CR.HSEBYP = 1;

RCC->CR.HSEON = 1;

while(!RCC->CR.HSERDY);

configurePLL();

RCC->CFGR.SW = SW PLL;

while (RCC->CFGR.SWS != 0b10);

SystemCoreClock = 84000000;

#ifndef STM32F4 RCC H

#define STM32F4 RCC H

#include <stdint.h>

```

```

uint32 t SystemCoreClock;

#define HSE VALUE 8000000

ST-LINK

#define IO volatile

#define RCC BASE (0x40023800UL) // base address of RCC

#define PLLSRC HSI 0

#define PLLSRC HSE 1

// Clock configuration

#define SW HSI 0

#define SW HSE 1

#define SW PLL 2

volatile uint32 t HSION : 1;

volatile uint32 t HSIRDY : 1;

: 1;

volatile uint32 t HSITRIM : 5;

volatile uint32 t HSICAL : 8;

volatile uint32 t HSEBYP : 1;

volatile uint32 t PLLRDY

volatile uint32 t PLLI2SON : 1;

volatile uint32 t PLLI2SRDY : 1;

```

```

typedef struct {

volatile uint32 t PLLN

: 1;

volatile uint32 t PLLP

: 1;

volatile uint32 t PLLQ

typedef struct {

volatile uint32 t HPRE

: 2;

volatile uint32 t PPRE1

volatile uint32 t RTCPRE : 5;

volatile uint32 t I2SSCR : 1;

volatile uint32 t MCO2PRE : 3;

volatile uint32 t GPIOAEN : 1;

volatile uint32 t GPIOBEN : 1;

volatile uint32 t GPIOCEN : 1;

volatile uint32 t GPIOEEN : 1;

volatile uint32 t CRCEN : 1;

```

```

volatile uint32 t TIM4EN : 1;

volatile uint32 t

: 2;

volatile uint32 t SPI3EN : 1;

volatile uint32 t USART2EN : 1;

volatile uint32 t I2C1EN : 1;

volatile uint32 t PWREN

volatile uint32 t USART6EN : 1;

: 2;

volatile uint32 t SPI1EN : 1;

volatile uint32 t SPI4EN : 1;

volatile uint32 t SYSCFGEN : 1;

: 1;

```

```

volatile uint32 t TIM10EN : 1;

volatile uint32 t TIM11EN : 1;

typedef struct {

Address offset: 0x00 */

IO PLLCFGR bits PLLCFGR; /*! < RCC PLL configuration register,

Address offset: 0x04 */

IO CFGR bits CFGR;

Address offset: 0x08 */

Address offset: 0x0C */

IO uint32 t AHB1RSTR;

register,

register,

IO uint32 t AHB3RSTR;

register,

RESERVEDO;

register,

register,

uint32 t RESERVED1[2]; /*!< Reserved, 0x28-0x2C

register,

register,

register,

uint32 t

RESERVED2; /*!< Reserved, 0x3C

register,

```

```

RESERVED3[2]; /*!< Reserved, 0x48-0x4C

in low power mode register, Address offset: 0x50 */

__IO uint32_t AHB2LPENR; /*!< RCC AHB2 peripheral clock enable

in low power mode register, Address offset: 0x54 */

IO uint32 t AHB3LPENR; /*!< RCC AHB3 peripheral clock enable

in low power mode register, Address offset: 0x58 */

uint32 t

IO uint32 t APB1LPENR; /*!< RCC APB1 peripheral clock enable

in low power mode register, Address offset: 0x60 */

IO uint32 t APB2LPENR; /*!< RCC APB2 peripheral clock enable

in low power mode register, Address offset: 0x64 */

uint32 t

RESERVED5[2]; /*!< Reserved, 0x68-0x6C

BDCR;

register,

register,

uint32 t RESERVED6[2]; /*!< Reserved, 0x78-0x7C

generation register,

IO uint32 t PLLI2SCFGR; /*!< RCC PLLI2S configuration register,

Address offset: 0x84 */

* /

register,

} RCC TypeDef;

#define RCC ((RCC TypeDef *) RCC BASE)

```

```

void configurePLL();

void configureClock();

#endif

#include "STM32F401RE ADC.h"

void configureADC(){

ADC1 -> CR2.ADON = 1;

ADC1->SQR1 \mid = (0b0000 << 20);

ADC1->SQR3 |= 0b00000;

ADC1->CR2.CONT = 0;

to DMA

ADC1->CR1.EOCIE = 1;

ADC1 -> CR2 \cdot EOCS = 1;

ADC1 - > CR2.SWSTART = 1;

#ifndef STM32F4 ADC H

#define STM32F4 ADC H

#include <stdint.h> // Include stdint header

```

```

#define ADC1 BASE (0x40012000UL)

#define IO volatile

// Bitfield structs

typedef struct {

IO uint32 t EOCIE

: 1;

: 1;

: 1;

: 2;

typedef struct {

IO uint32 t ADON

: 1;

: 1;

: 1;

: 1;

```

```

__IO uint32_t JEXTSEL : 4;

typedef struct {

IO uint32 t : 16;

typedef struct {

0x00 */

0x04 */

0x08 */

0x0C */

0x10 */

0x14 */

0x18 */

0x1C */

0x20 */

0x24 */

0x28 */

```

```

IO uint32 t SQR1; /*!< ADC SQR1

0x2C */

0x30 */

__IO uint32 t JSQR; /*!< ADC JSQR

0x3C */

0x40 */

0x44 */

0x48 */

0x4C */

ADC TypeDef;

// Pointers to ADC-sized chunks of memory for each peripheral

#define ADC1 ((ADC TypeDef *) ADC1 BASE)

void configureADC();

#endif

// STM32F401RE SPI.c

// SPI function declarations

#include "STM32F401RE SPI.h"

#include "STM32F401RE RCC.h"

#include "STM32F401RE GPIO.h"

^{\prime *} Enables the SPI peripheral and intializes its clock speed (baud rate),

polarity, and phase.

2^{(BR+1)}.

state is logical 1).

```

```

captured on next edge,

edge)

settings:

void spiInit(uint32 t br, uint32 t cpol, uint32 t cpha) {

AHB1ENR)

RCC->AHB1ENR.GPIOAEN = 1;

RCC->APB2ENR.SPI1EN = 1; // Turn on SPI1 clock domain (SPI1EN bit in

pinMode(GPIOA, 5, GPIO ALT); // PA5, Arduino D13, SPI1 SCK

pinMode(GPIOA, 7, GPIO ALT); // PA7, Arduino D11, SPI1 MOSI

pinMode(GPIOA, 1, GPIO OUTPUT); // PB6, Arduino D10, Manual CS

// Set to AF05 for SPI alternate functions

GPIOA->AFRL \mid = (1 << 22) \mid (1 << 20);

GPIOA -> AFRL \mid = (1 << 30) \mid (1 << 28);

GPIOA->AFRL |= (1 << 18) | (1 << 16);

SPI1->CR1.BR = br; // Set the clock divisor

SPI1->CR1.CPOL = cpol; // Set the polarity

SPI1->CR1.CPHA = cpha; // Set the phase

SPI1->CR1.LSBFIRST = 0; // Set least significant bit first

SPI1->CR1.DFF = 1;

SPI1->CR1.SSM = 0;

SPI1->CR1.MSTR = 1;

```

```

SPI1->CR1.SPE = 1;  // Enable SPI

uint16 t spiSendReceive16(uint16 t send) {

digitalWrite(GPIOB, 6, 0);

SPI1->CR1.SPE = 1;

SPI1->DR.DR = send;

while(!(SPI1->SR.RXNE));

uint16 t rec = SPI1->DR.DR;

SPI1->CR1.SPE = 0;

digitalWrite(GPIOB, 6, 1);

return rec;

uint16 t spiSendReceive12(uint16 t send) {

while(SPI1->SR.TXE != 0b1){} // wait until the transmission buffer is

empty

digitalWrite(GPIOA, 1, 0);

SPI1->CR1.SPE = 1;

```

```

uint16 t modified send = (0b0001 << 12) | (send & 0xFFF);</pre>

SPI1->DR.DR = modified send;

while(!(SPI1->SR.RXNE));

uint16 t rec = SPI1->DR.DR;

SPI1->CR1.SPE = 0;

digitalWrite(GPIOA, 1, 1);

return rec;

#ifndef STM32F4 SPI H

#define STM32F4 SPI H

#include <stdint.h> // Include stdint header

#define SPI1 BASE (0x40013000UL)

#define IO volatile

typedef struct {

: 1;

: 1;

IO uint32 t SPE

: 1;

```

```

IO uint32 t LSBFIRST : 1;

: 1;

: 1;

: 16;

typedef struct {

: 1;

__IO uint32_t RXNEIE : 1;

: 24;

: 1;

: 1;

: 1;

: 1;

: 1;

: 1;

: 1;

: 16;

```

```

typedef struct {

typedef struct {

I2S mode), Address offset: 0x00 */

Address offset: 0x04 */

Address offset: 0x08 */

Address offset: 0x0C */

I2S mode), Address offset: 0x10 */

mode),

mode), Address offset: 0x18 */

Address offset: 0x1C */

Address offset: 0x20 */

SPI TypeDef;

// Pointers to GPIO-sized chunks of memory for each peripheral

#define SPI1 ((SPI TypeDef *) SPI1 BASE)

^{\prime *} Enables the SPI peripheral and intializes its clock speed (baud rate),

```

```

state is logical 1).

void spiInit(uint32 t clkdivide, uint32 t cpol, uint32 t ncpha);

uint16 t spiSendReceive16(uint16 t send);

uint16 t spiSendReceive12(uint16 t send);

#endif

```

<sup>\*</sup>We did not include USART, or GPIO libraries as they were not modified at all from the ones given to us in the course.