# MC You

E155 Final Project

December 10, 2021

Santiago Rodriguez and Kariessa Schultz

# **Abstract**

The goal of this project was to create an audio-mixing station which uses two stepper motors to play a song and plays beat sequences according to user input on a speaker. To create this system, we used the STM32F401RE microcontroller (MCU) and the MAX1000 board (FPGA). We wrote an I2C driver for the MCU to talk to a digital-to-analog converter (DAC), developed two novel encodings: one to hold the stepper motor audio data and the other for the FPGA to send the MCU commands over SPI, and wrote multiple finite state machines on the FPGA to process user input. We also created a custom box to hold our breadboards, MCU, and FPGA, to present a nicer interface for the user. The microcontroller is responsible for keeping track of the system's state including remembering two sequences of beats entered by the user, whether or not the stepper motor song is playing, and the current progress through the song. The FPGA handles user input, processing sequences of switch presses into abstract syntax which is sent to the MCU over an SPI link.

# Introduction

Music production and consumption is higher than ever. We wanted to make a musical product that would allow people to play with a song in ways like a DJ. This is how we came up with functionality like putting beats over the song and jumping back to a specific point in time in the song. Inspired by the creativity of some artists on Youtube, we decided to use stepper motors to play our music.

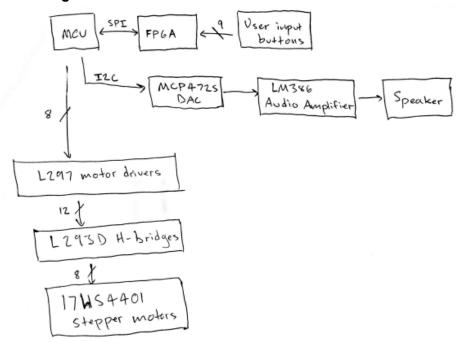

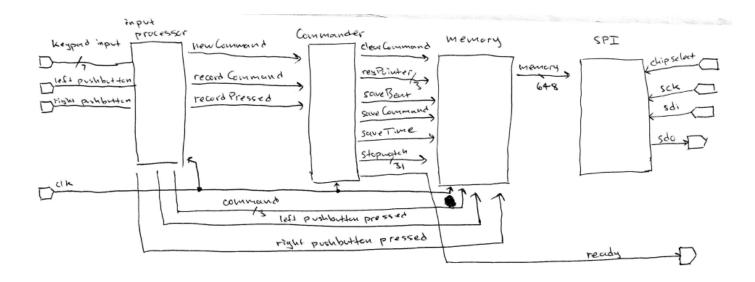

The top-level diagram of the system is shown in Figure 1. The user presses the buttons (a matrix keypad and two recording buttons), and the resulting signals are sent to the FPGA. See Figure 2 for the available user commands.

The FPGA handles switch bounce and, if the user is recording a sequence, stores the series of button presses and the times between each press in memory. The FPGA converts this data into byte-long commands which are sent to the MCU over SPI. If the command indicates that there is a sequence to be read, then the MCU will keep running the SPI until it retrieves all of the data from the FPGA. The MCU then responds appropriately by updating its state, which is a set of global variables controlling its behavior and the saved beat sequences. In the MCU's main function, it uses time multiplexing to send audio data over an I2C link to the DAC in parallel with PWM signals to the motor drivers. This outputs sequences of beats on the speaker and determines the specific note that the motors play, respectively. Interrupts handle the inputs to the MCU from the FPGA and govern the speaker and stepper motor behavior accordingly.

### **Block diagram**

Figure 1. High level block diagram showing the flow of data through the system

| User input                                                              | Desired function                                                                                                                    | Single byte encoding sent over SPI |

|-------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------|------------------------------------|

| Press left record switch, followed by a sequence of keys on the keypad  | Record all presses of '1', '2', and '3' keys on the keypad and the times between them, and save this data in the MCU in save slot 1 | 0x05                               |

| Press right record switch, followed by a sequence of keys on the keypad | Record all presses of '1', '2', and '3' keys on the keypad and the times between them, and save this data in the MCU in save slot 2 | 0x06                               |

| Press key '4'                                                           | Play the sequence saved in save slot 1                                                                                              | 0x07                               |

| Press key '5'                                                           | Play the sequence saved in save slot 2                                                                                              | 0x08                               |

| Press key '7'                                                           | Repeatedly play the sequence saved in save slot 1, or stop playing it on repeat                                                     | 0x09                               |

| Press key '8'                                                           | Repeatedly play the sequence saved in save slot 2, or stop playing it on repeat                                                     | 0x0A                               |

| Press key '6'                                                           | Pause or resume stepper motor song                                                                                                  | 0x0D                               |

| Press key '9'                                                           | Play stepper motor song from beginning                                                                                              | 0x04                               |

| Press key '*'                                                           | Mark spot in stepper motor song                                                                                                     | 0x0C                               |

| Press key '0'                                                           | Go back to marked spot in stepper motor song                                                                                        | 0x0B                               |

Figure 2. Table showing available user commands, what they do, and how they are internally encoded

# Hardware Overview

#### **New hardware**

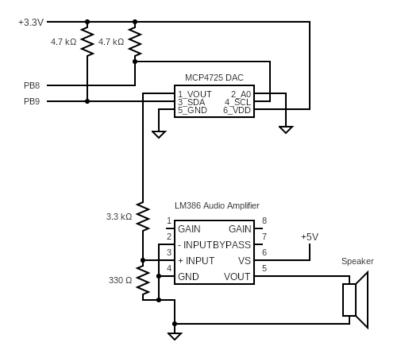

To play the sequences of beats on a speaker, we use a MCP4725 digital-to-analog converter (DAC) attached to a LM386 audio amplifier. The MCU sends the desired output voltage to the DAC over an I2C link. All devices on an I2C link use the same data wire (SDA) to communicate, with a clock wire (SCK) controlling when to read input from the data wire. In order to communicate with the DAC, the MCU first sends the DAC's address over SDA, waits for an ACK bit which indicates that the DAC has seen its address and is listening, and then sends another byte which tells the DAC what its output voltage should be. The DAC also ACKs the voltage byte.

This communication is relatively slow, at about 400 Kbps. Considering that our audio sampling rate is 8 KHz, the I2C's SDA is almost always active while the MCU is playing a beat.

The LM386 then amplifies the DAC's voltage signals into a large waveform which is played by the speaker.

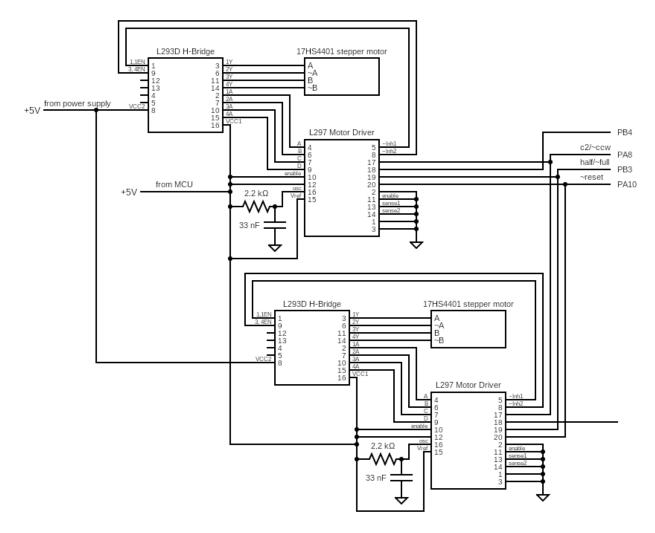

To generate the sound for our song, we use stepper motors. These motors are composed of permanent magnets which are turned by electromagnets. Pulses are sent to the motor to turn the rotors by magnifying different stators across the sides. There are some teeth along the inside which the rotors click against. By controlling the frequency that the rotors turn, we can play different notes which is how we generate the music for our song. We use two stepper motors to have a bass line and a treble line, but they are easily interchangeable.

In order to get the motors to turn at the right frequency, we use L297 motor drivers and L293D H-bridges. The motor driver takes in a frequency generated by the MCU and maps it to the correct signals to send to the motor to turn the motor at that frequency. The H-bridge takes care of making sure that the right stators are powered as the driver dictates and makes sure they have enough power to turn. We attached a power supply to the circuit to power the H-bridges so that we wouldn't draw too much current from the MCU. Additionally, the motor drivers are used to set the motors in half step mode as opposed to full step mode.

### **Schematics**

PIN\_E3

PIN\_K10

15 kΩ

Figure 3. Speaker and DAC circuit diagram. The DAC takes input from the MCU over an I2C link and adjusts its voltage output appropriately. The audio amplifier amplifies the DAC's signal and sends it to the speaker.

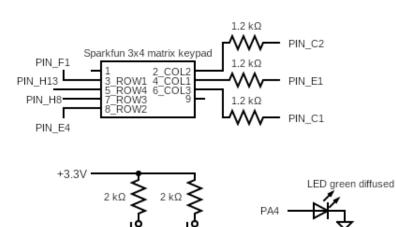

Figure 4. User interface circuit diagram. Input from the keypad and switches is sent to the FPGA for processing. The green diffused LED turns on when the MCU is finished with the initialization steps and the system is ready to use.

**Figure 5**. Stepper motor circuit diagram. The MCU controls the stepper motors by sending a clock signal to the motor drivers. These, along with the H-bridges, power the stators in the motors at the right frequency to play notes.

# MCU Design

The MCU sends signals to the DAC to tell it to change its output voltage level in order to play the beats on the speaker. Because the MCU communicates with the DAC over a 400 Kbps I2C link, and our audio sampling rate is 8 Khz, when playing a beat, the MCU spends most of its time waiting for the ACK bit from the DAC telling the MCU that the DAC has received the command. Because the beat audio data is noise-tolerant (it does not matter if we send a frame a little bit late), we made this functionality our main loop.

All other functionality is implemented using interrupts.

The MCU takes care of initializing the stepper motors and changing their frequency. To do this, we use a timer (TIM2) that sends an interrupt to change the note values for the stepper motors

at 16th note intervals. 16th notes are commonly the subdivision of the beat of a song by four. This allows us to control the duration of the notes with precision. When the interrupt occurs, 2 separate timers (TIM3 and TIM4) output the correct frequency for the note they are supposed to play to the motor driver. They get the frequency from a list specific to each timer that has the frequencies for each 16th note in the song. The index of the lists is incremented every time the interrupt is sent by TIM2 to advance the lists through the song. TIM3 and TIM4 have their clocks prescaled to a smaller frequency because they don't have enough bits to count to to output the right frequencies otherwise.

The MCU also responds to user commands from the FPGA (see table 1.2 for the full list). The FPGA raises the voltage level of PA1 to tell the MCU that there is data to be read over SPI. When PA1's voltage goes high, it triggers an interrupt on the MCU. The MCU then reads a byte from the FPGA over SPI and decodes it, according to the list of functionality in Figure 2.

For the non-recording user commands, the MCU updates a set of global variables. To pause the song and play it again from the paused point, we simply turn off all the timer counters which stopped them at their current values. Turning the counters on again for each timer starts it right where it left off. To mark a point and go back to a marked point in a song, we kept track of how far TIM2 is in the process of counting a 16th note. If a user pauses somewhere in the middle, we want to make sure it starts off at the exact same point. To do this we store the timer value of TIM2 and the index of the song notes lists and return to those values when going back to that marked point.

For the recording commands, the MCU then reads in another 640 bytes from the FPGA over the SPI link, interpreting them as an array of [beat, time] data, where the beat is an eight bit encoding telling the MCU what beat to play, and the time is a 32-bit integer representing how long to wait after starting playing the beat until playing the next one. Because the time is in FPGA clock cycles (12 MHz), the MCU will convert the time to milliseconds before saving it in the data structure for the appropriate beat sequence.

# **FPGA Design**

The FPGA design consists of four main parts: an SPI module, an input processor module, a memory module, and a commander module. See Figure 6 for the high level design.

The input processor module is responsible for processing user input into a reliable internal representation. It consists of four submodules. One debounces the user input, signals the commander when new input has been observed with the *newCommand* signal, and also signals the commander whether or not that input is one of the recording buttons (keys '1,' '2,' or '3') with the *recordCommand* signal. Another turns the matrix keypad inputs into a four bit internal representation. Two other modules debounce the pushbutton inputs, one for each pushbutton. Each debouncer module works the same way. After a change in input has been observed, they go to an intermediate state and wait to make sure that the change in input is genuine before transitioning to a different state in order to tell the rest of the system what the input is.

The SPI module shifts out the contents of the memory when it sees the clock line from the MCU (sck) enabled. To do this, it has a shift register which resets to the contents of the memory on the edge of sck when the data input line (sdi) goes high. This design is particularly useful because it allows for code reuse. In one case, the SPI must output the single byte command. In the other case, the SPI must output the single byte command and then keep outputting the rest of the memory. By resetting whenever sdi goes high, a single SPI module is able to handle both behaviors, without worrying about how many bytes have been read by the MCU or how many bytes there are left to be read. As a consequence, when reading the SPI's memory, the MCU must always output 0x10 on the sdi line when starting a new read, and the rest of the bytes it sends must be 0x00.

The memory module is 648 bits of registers. The first byte is the first byte to be sent to the FPGA. This command is the same as the internal representation of the keypad commands, as long as a record button has not been pressed. When a record button is pressed and *saveCommand* is asserted, the memory module will instead save a different byte, to tell the MCU that it needs to read the rest of the memory in order to get the rest of the new beat sequence. The next 640 bits are arranged as a sequence of [beat, time], where the beat is a single byte encoding -- either 0x01, 0x02, or 0x03 for a real beat, or 0x0F for an empty register -- and the time is a 32 bit integer, with the FPGA's clock cycles as a unit. Each [beat, time] pair is implemented as a pair of enabled registers. The current value of *regPointer*, updated by the commander, determines which register pair is enabled when *saveCommand* is asserted. Only one register pair is enabled at a time. Also, when the *clearCommand* input is inserted, the memory module will save 0x0F in the beat register instead of the last keypad button pressed. When the MCU reads in 0x0F, it will know that it is not a valid beat and it can stop playing the sequence. This allows the FPGA to store any number of beats, up to a maximum of 16.

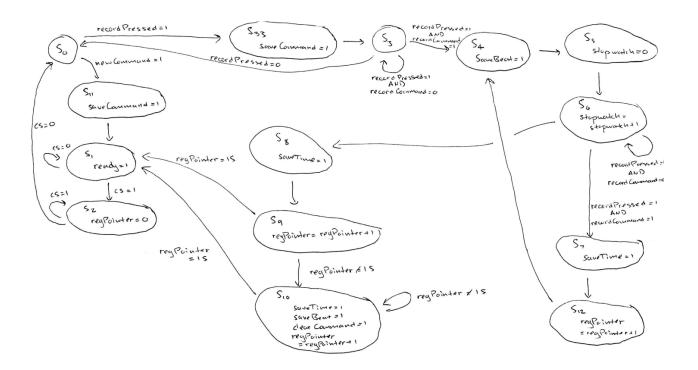

The commander module is a finite state machine responsible both for updating the memory and for signalling the MCU to read the memory over SPI. See Figure 7 for a detailed diagram of the states, transitions, and outputs. If neither record button is pressed, then the commander simply detects when there is a new input from the keypad, asserts saveCommand to tell the memory module to save the command in the memory that will be sent out to SPI, and asserts the ready signal to tell the MCU that there is input to be read over SPI. It will deassert ready once the input has been read. If a record button is pressed, then the commander asserts saveCommand to tell the memory module to save the record command, then waits for recordCommand to be asserted, meaning that a key on the keypad has been pressed. It then transitions to another state where it increments a stopwatch to measure how much time passes between beats. When recordCommand is asserted again, then the commander increments regPointer, asserts saveCommand to tell the memory module to save the current beat and time, and transitions back to the stopwatch state. When a record button is no longer pressed, if 16 beats have been entered, then the commander either asserts the ready signal and waits for the SPI transition to be over. Otherwise, it transitions to another state, asserts clearCommand, and increments regPointer until the rest of the registers have been cleared by the memory module.

Figure 6. High level overview of FPGA modules and data flow.

**Figure 7.** Commander finite state machine, with states, transitions, and outputs. Outputs are set to zero by default. For example, in the S0 state, saveCommand is equal to 0.

# Results and Discussion

In the end, our system performed all of its tasks as listed in the revised project proposal. Our project was able to play a song of about 2 minutes and 15 seconds on stepper motors, start the song from the beginning at any time, pause/play the song, mark a point to jump back to, record sequences of beats to play on the speaker, play up to two saved sequences of beats on the speaker, and loop the sequences of beats on the speaker.

At the very end, we noticed some issues with the motors making a grinding sound when they weren't supposed to. We suspect that either the chips might have been heating up after being powered for too long, or the motors were drawing too much current from the power supply and needed to be regulated by lowering the voltage.

We also encountered some problems related to the wiring when assembling the final box, due to wires coming loose or coming in contact with each other. In the future, we would like to clean up the wiring so less wires cross each other, try to put all of the hardware on one breadboard, and clip the stripped sections of the wires so they are less likely to contact each other.

All in all, it is a fun system that plays a cool song and allows users to act like a DJ just as intended.

## References

- "12-Bit Digital-to-Analog Converter with EEPROM Memory in SOT-23-6 Datasheet." Microchip.

- 2. "2 Phase Hybrid Stepper Motor 17HS4401." MotionKing (China) Motor Industry Co.

- 3. "External Interrupt Using Registers " Controllerstech." *ControllersTech*, 15 July 2021, https://controllerstech.com/external-interrupt-using-registers/.

- 4. "L293x Quadruple Half-H Drivers Datasheet." Texas Instruments, Jan. 2016.

- 5. "The L297 Stepper Motor Controller User Guide." ST.

- 6. "L297 Stepper Motor Controllers Datasheet." ST.

- 7. SFUptownMaker. "I2C." Sparkfun, https://learn.sparkfun.com/tutorials/i2c/all.

- 8. "'Bare Metal' STM32 Programming (Part 4): Intro to Hardware Interrupts." *Vivonomicon's Blog*,

https://vivonomicon.com/2018/04/28/bare-metal-stm32-programming-part-4-intro-to-hard ware-interrupts/.

# **Bill of Materials**

| Item        | Quantity | Manufacturer     | Cost per unit | Total cost |

|-------------|----------|------------------|---------------|------------|

| MCP4725 DAC | 1        | Adafruit         | \$4.95        | \$4.95     |

| MAX1000     | 1        | Trenz Electronic | \$26.66       | \$26.66    |

| Nucleo-F401RE                            | 1 | STM                               | \$13.83 | \$13.83 |

|------------------------------------------|---|-----------------------------------|---------|---------|

| MAX1000 Shield<br>PCB                    | 1 | OSH Park                          | \$6.80  | \$6.80  |

| Breadboard<br>Cobbler PCB                | 1 | OSH Park                          | \$6.24  | \$6.24  |

| Stackable headers kit                    | 1 | SparkFun<br>Electronics           | \$1.50  | \$1.50  |

| 40-pin male<br>breakable<br>header       | 2 | Sullins<br>Connector<br>Solutions | \$0.51  | \$1.02  |

| 40-pin keyed ribbon cable                | 1 | Assman WSW<br>Components          | \$1.66  | \$1.66  |

| 40-pin male<br>vertical keyed<br>header  | 2 | Sullins<br>Connector<br>Solutions | \$0.73  | \$1.46  |

| 14-pin female<br>headers                 | 2 | Sullins<br>Connector<br>Solutions | \$0.91  | \$1.82  |

| USB A to Mini B<br>Cable White, 3 ft     | 1 | Monoprice                         | \$1.21  | \$1.21  |

| USB A to Micro<br>B Cable Black, 3<br>ft | 1 | Monoprice                         | \$0.99  | \$0.99  |

| L293D H-bridge                           | 2 | Adafruit                          | \$4.50  | \$9.00  |

| 17HS4401<br>Stepper motor                | 2 | Usongshine                        | \$9.98  | \$19.96 |

| L297 stepper motor driver                | 2 | STMicroelectroni<br>cs            | \$4.89  | \$9.78  |

| 3x4 matrix<br>keypad                     | 1 | SparkFun<br>Electronics           | \$4.50  | \$4.50  |

| Pushbutton switch                        | 2 | Allied<br>Electronics             | \$3.36  | \$6.72  |

| LM386 audio amplifier                    | 1 | Texas<br>Instruments              | \$1.50  | \$3.00  |

| 47000 ohm<br>resistor                    | 2 | Jameco<br>Electronics             | \$0.14  | \$0.28  |

| 3300 ohm<br>resistor  | 1 | JMar Vac<br>Electronics | \$1.79 | \$1.79 |

|-----------------------|---|-------------------------|--------|--------|

| 330 ohm resistor      | 1 | Jameco<br>Electronics   | \$0.14 | \$0.14 |

| speaker               | 1 | Philmore                | \$4.53 | \$4.53 |

| 1200 ohm<br>resistor  | 3 | Jameco<br>Electronics   | \$0.06 | \$0.12 |

| 2000 ohm<br>resistor  | 2 | All Electronics         | \$0.06 | \$0.12 |

| 15000 ohm resistor    | 2 | Jameco<br>Electronics   | \$0.06 | \$0.12 |

| Green diffused<br>LED | 1 | Jameco<br>Electronics   | \$0.06 | \$0.12 |

| 2200 ohm<br>resistor  | 2 | Jameco<br>Electronics   | \$0.06 | \$0.12 |

| 33 nF capacitor       | 2 | Mouser<br>Electronics   | \$0.36 | \$0.72 |

### Appendix A: C code

#### Main.c

```

#include <stdint.h>

#include "audio data.h"

#include "STM32F401RE TIM2 5.h"

#include "STM32F401RE TIM10 11.h"

#include "STM32F401RE GPIO.h"

#include "STM32F401RE RCC.h"

#include "STM32F401RE FLASH.h"

#include "STM32F401RE I2C.h"

#include "STM32F401RE EXTI.h"

#include "STM32F401RE SPI.h"

#include "main.h"

#include "STM32F401RE SYSCFG.h"

#include "songs.h"

volatile uint8 t stepper song is paused = 1; // song is paused by default

volatile uint32 t stepper marked index = 0;

// for pause points

volatile uint16 t stepper song index = 0;

volatile uint32 t stepper tim position = 0; // value of the timer

register when paused

volatile uint8 t play seq one once = 0;

volatile uint8 t play seq two once = 0;

volatile uint8 t repeat seq one = 0;

volatile uint8 t repeat seq two = 0;

```

```

static uint8 t DAC ADDRESS = 0b11000100;

static uint8 t MAX NUMBER OF BEATS = 16;

enum BeatChoice {ZERO, ONE, TWO, NONE};

typedef struct {

uint16 t rest;

represent up to just over a minute

enum BeatChoice beat;

SeqElement;

SeqElement seq one[16];

SeqElement seq two[16];

#define NULL 0

interrupts

void configureInterrupts(void) {

RCC->APB2ENR \mid = (1<<14);

SYSCFG->EXTICR1 &= \sim (0xf << 4);

EXTI->IMR |= (1 << 1);

EXTI->RTSR \mid = (1<<1);

EXTI->FTSR &= \sim (1 << 1);

NVIC SetPriority (EXTI1 IRQn, 0);

```

```

NVIC SetPriority(TIM2 IRQn, 2);

NVIC EnableIRQ(TIM2 IRQn);

void readBeatsAndTimes(SeqElement sequence[]) {

uint8 t beat = spiSendReceive(0x00);

if (beat == 1) {

sequence[i].beat = ZERO;

} else if (beat == 2) {

sequence[i].beat = ONE;

sequence[i].beat = TWO;

sequence[i].beat = NONE;

uint32 t time = spiSendReceive(0x00);

time = time << 8;

time = time + spiSendReceive(0x00);

time = time << 8;

time = time + spiSendReceive(0x00);

time = time << 8;</pre>

time = time + spiSendReceive(0x00);

sequence[i].rest = (time) / (12000); // convert 12 Mhz clock

roid EXTI1 IRQHandler(void)

```

```

EXTI->PR |= (1 << 1);

uint8 t command = spiSendReceive(0x80);

if (command == 0x0D) {

if (!stepper song is paused) {

TIM2 - > CR1.CEN = 0;

TIM3->CR1.CEN = 0;

TIM4->CR1.CEN = 0;

TIM2 - > CR1.CEN = 1;

TIM3->CR1.CEN = 1;

TIM4->CR1.CEN = 1;

stepper song is paused = !stepper song is paused;

stepper tim position = TIM2->CNT;

stepper marked index = stepper song index;

TIM2 -> CR1.CEN = 0;

TIM2->CNT = stepper tim position;

TIM2 -> CR1.CEN = 1;

changeMotorPWM(TIM3, song[stepper marked index]);

changeMotorPWM(TIM4, song2[stepper marked index]);

stepper song index = stepper marked index;

} else if (command == 0x04) {

TIM2 -> CR1.CEN = 0;

TIM2 -> CNT = 0;

TIM2 -> CR1.CEN = 1;

changeMotorPWM(TIM3, song[0]);

changeMotorPWM(TIM4, song2[0]);

TIM3->CR1.CEN = 1;

TIM4->CR1.CEN = 1;

```

```

stepper song index = 0;

stepper song is paused = 0;

readBeatsAndTimes(seq one);

} else if (command == 0x06) {

readBeatsAndTimes(seq two);

play seq one once = 1;

} else if (command == 0x08) {

play seq two once = 1;

repeat seq one = !repeat seq one;

repeat seq two = !repeat seq two;

roid TIM2 IRQHandler(void) {

```

```

if (TIM2->SR.CC1IF == 1) {

TIM2->SR.CC1IF = 0;

if (!stepper song is paused) {

changeMotorPWM(TIM3, 2*song[stepper_song_index]);

changeMotorPWM(TIM4, 2*song2[stepper_song_index]);

stepper song index++;

if (stepper song index > sizeof(song)/sizeof(song[0])) {

stepper song index = 0;

stepper song is paused = 1;

changeMotorPWM(TIM3, 0);

changeMotorPWM(TIM4, 0);

void resetRestOfSequence(SeqElement sequence[], uint8 t index) {

sequence[i].beat = NONE;

uint8 t* selectAudioData(enum BeatChoice number, int* arraySize) {

if (number == ZERO) {

(*arraySize) = sizeof(notes1)/sizeof(notes1[0]);

return notes1;

} else if (number == ONE) {

*arraySize = sizeof(notes2)/sizeof(notes2[0]);

return notes2;

} else if (number == TWO) {

```

```

*arraySize = sizeof(notes3)/sizeof(notes3[0]);

return notes3;

void initializeAll(void) {

configureFlash();

configureClock();

RCC->AHB1ENR.GPIOAEN = 1;  // GPIOA

RCC->APB1ENR |= 1;

RCC->APB1ENR \mid= (1 << 3); // TIM5

RCC->APB1ENR \mid = (1<<21);

RCC->APB2ENR |= (1<<17);  // TIM10

RCC->APB2ENR \mid = (1 << 14);

pinMode(GPIOA, 10, GPIO OUTPUT); // ~reset

pinMode(GPIOB, 3, GPIO OUTPUT); // half/~full

pinMode (GPIOA, 8, GPIO OUTPUT); // CW/~CCW USE PA8 for GPIO instead,

pinMode(GPIOB, 6, GPIO ALT); // TIM4

GPIOB->AFRL |= (2 << 24);

pinMode(GPIOA, 15, GPIO ALT);  // set pin 15 as alternate function

GPIOA->AFRH \mid = (1 << 28); // set pin 15 alternate function as

pinMode(GPIOB, 4, GPIO ALT);

GPIOB->AFRL |= (2 << 16);

```

```

pinMode(GPIOA, 3, GPIO INPUT); // ready pin

pinMode(GPIOA, 4, GPIO OUTPUT); // LED

pinMode(GPIOB, 8, GPIO ALT); // SCL

pinMode(GPIOB, 9, GPIO ALT);  // SDA

GPIOB->AFRH |= 0b0100;

GPIOB->AFRH |= 0b0100 << 4;

GPIOB->OSPEEDR |= (3 << 16) | (3 << 18); // select high speed

setPinToOpenDrain(GPIOB, 8);

setPinToOpenDrain(GPIOB, 9);

configureInterrupts();

spiInit(1, 0, 0);

configureTimer1011(TIM10);

configureLongARRTimer(TIM5);

configureMotorTimer(TIM3);

configureMotorTimer(TIM4);

configureDurationTimer(TIM2);

TIM3->CR1.CEN = 0;

TIM4->CR1.CEN = 0;

configureI2C();

enable I2C();

I2C general call reset();

disable I2C();

```

```

resetRestOfSequence(seq one, 0);

resetRestOfSequence(seq two, 0);

digitalWrite(GPIOB, 3, 1);

digitalWrite(GPIOB, 4, 1);

digitalWrite(GPIOA, 10, 1);

digitalWrite(GPIOA, 10, 0);

digitalWrite(GPIOA, 10, 1);

void playSequence(SeqElement sequence[]) {

for (int i = 0; i < MAX NUMBER OF BEATS; ++i) {</pre>

if (sequence[i].beat != NONE) {

setTimerFromFreq1011(TIM10, 8000);

setTimerFromTime(TIM5, sequence[i].rest);

TIM5->SR.CC1IF = 0;

int numFrames;

uint8 t* frameArray = selectAudioData(sequence[i].beat,

&numFrames);

int frameIndex = 0;

enable I2C();

if (frameIndex > numFrames - 1) {

```

```

if (TIM10->SR.CC1IF == 1) {

TIM10->SR.CC1IF = 0;

uint16 t frame = frameArray[frameIndex] << 4;</pre>

frameIndex += 1;

disable I2C();

if (TIM5->SR.CC1IF == 1) {

TIM5->SR.CC1IF = 0;

int main(void) {

initializeAll();

digitalWrite(GPIOA, 4, 1); // turn LED green

while(1) {

if (play seq one once) {

playSequence(seq one);

play seq one once = 0;

} else if (play seq two once) {

playSequence(seq two);

play_seq_two_once = 0;

while (repeat_seq_one) {

playSequence(seq one);

while (repeat seq two) {

```

```

playSequence(seq_two);

}

}

```

#### Main h

```

#ifndef MAIN H

#define MAIN H

#define LED PIN 5

#define BUTTON PIN 13 // PC13

#define DELAY TIM TIM2

#define NVIC ISER0 ((uint32 t *) 0xE000E100UL)

#define NVIC ISER1 ((uint32 t *) 0xE000E104UL)

#define SYSCFG EXTICR4 ((uint32 t *) (0x40013800UL + 0x14UL))

```

```

BusFault IRQn

Interrupt

Interrupt

SVCall IRQn

Interrupt

WWDG IRQn

PVD IRQn

detection Interrupt

TAMP STAMP IRQn

interrupts through the EXTI line

the EXTI line

```

```

EXTI3 IRQn

EXTI4 IRQn

DMA1 Stream0 IRQn

= 11,

= 12,

= 14, /*!< DMA1 Stream 3 global Interrupt

= 15, /*!< DMA1 Stream 4 global Interrupt

= 16, /*!< DMA1 Stream 5 global Interrupt

= 18,

= 24,

= 25,

TIM1 TRG COM TIM11 IRQn = 26,

= 27, /*!< TIM1 Capture Compare Interrupt

TIM2 IRQn

= 28,

= 30, /*!< TIM4 global Interrupt

```

```

I2C2 EV IRQn

= 34, /*!< I2C2 Error Interrupt

= 36, /*!< SPI2 global Interrupt

line interrupt

= 49, /*!< SDIO global Interrupt

= 56, /*!< DMA2 Stream 0 global Interrupt

DMA2 Stream0 IRQn

DMA2 Stream1 IRQn

DMA2 Stream2 IRQn

= 58, /*!< DMA2 Stream 2 global Interrupt

DMA2 Stream5 IRQn

```

#### STM32F401RE EXTI.h

### STM32F401RE FLASH.h

```

// STM32F401RE_FLASH.h

// Header for FLASH functions

#ifndef STM32F4_FLASH_H

#define STM32F4_FLASH_H

#include <stdint.h>

/////

// Definitions

//////

#define __IO volatile

// Base addresses for GPIO ports

#define FLASH_BASE (0x40023C00UL) // base address of RCC

```

```

IO uint32 t LATENCY :4;

:4;

IO uint32 t PRFTEN :1;

IO uint32 t ICEN :1;

IO uint32 t DCEN :1;

IO uint32 t DCRST :1;

IO uint32 t :19;

typedef struct {

offset: 0x00 */

IO uint32 t OPTKEYR; /*!< FLASH option key register,

offset: 0x0C */

IO uint32 t CR; /*!< FLASH control register,

offset: 0x10 */

IO uint32 t OPTCR; /*!< FLASH option control register , Address

offset: 0x14 */

IO uint32 t OPTCR1; /*! < FLASH option control register 1, Address

offset: 0x18 */

} FLASH TypeDef;

#define FLASH ((FLASH TypeDef *) FLASH BASE)

```

## STM32F401RE\_FLASH.c

```

// STM32F401RE_FLASH.c

// Source code for FLASH functions

#include "STM32F401RE_FLASH.h"

void configureFlash() {

FLASH->ACR.LATENCY = 2; // Set to 0 waitstates

FLASH->ACR.PRFTEN = 1; // Turn on the ART

}

```

### STM32F401RE GPIO.h

```

#define GPIOC BASE (0x40020800UL)

// Arbitrary GPIO functions for pinMode()

#define GPIO INPUT 0

#define GPIO OUTPUT 1

#define GPIO ALT 2

#define GPIO ANALOG 3

typedef struct {

volatile uint32 t AFRLO : 4;

volatile uint32 t AFRL1 : 4;

volatile uint32 t AFRL2 : 4;

volatile uint32 t AFRL3 : 4;

volatile uint32 t AFRL4 : 4;

volatile uint32 t AFRL5 : 4;

volatile uint32 t AFRL6 : 4;

volatile uint32 t AFRL7 : 4;

volatile uint32 t AFRH8 : 4;

volatile uint32 t AFRH9 : 4;

volatile uint32 t AFRH10 : 4;

volatile uint32 t AFRH11 : 4;

volatile uint32 t AFRH12 : 4;

volatile uint32 t AFRH13 : 4;

volatile uint32 t AFRH14 : 4;

volatile uint32 t AFRH15 : 4;

volatile uint32 t OTYPER; // GPIO Offset 0x04

```

```

volatile uint32 t OSPEEDR; // GPIO Offset 0x08

volatile uint32 t PURPDR; // GPIO Offset 0x0C

volatile uint32 t AFRH; // GPIO Offset 0x24

#define GPIOA ((GPIO TypeDef *) GPIOA BASE)

#define GPIOC ((GPIO TypeDef *) GPIOC BASE)

void pinMode(GPIO TypeDef *, int pin, int function);

int digitalRead(GPIO TypeDef *, int pin);

void digitalWrite(GPIO TypeDef *, int pin, int val);

void setPinToOpenDrain(GPIO TypeDef* GPIO PORT PTR, int pin);

void togglePin(GPIO TypeDef *, int pin);

#endif

```

### STM32F401RE GPIO.C

```

// STM32F401RE_GPIO.c

// Source code for GPIO functions

#include "STM32F401RE_GPIO.h"

void pinMode(GPIO_TypeDef* GPIO_PORT_PTR, int pin, int function) {

```

```

GPIO PORT PTR->MODER &= ~(0b11 << 2*pin);

case GPIO OUTPUT:

GPIO PORT PTR->MODER |= (0b1 << 2*pin);

GPIO PORT PTR->MODER &= \sim (0b1 << (2*pin+1));

GPIO PORT PTR->MODER &= ~(0b1 << 2*pin);

GPIO PORT PTR->MODER |= (0b1 << (2*pin+1));</pre>

GPIO PORT PTR->MODER |= (0b11 << 2*pin);

void setPinToOpenDrain(GPIO TypeDef* GPIO PORT PTR, int pin) {

GPIO PORT PTR->OTYPER |= (1 << pin);

int digitalRead(GPIO TypeDef* GPIO PORT PTR, int pin) {

return ((GPIO PORT PTR->IDR) >> pin) & 1;

void digitalWrite(GPIO TypeDef* GPIO PORT PTR, int pin, int val) {

if(val == 1) {

GPIO PORT PTR->ODR |= (1 << pin);

else if(val == 0) {

GPIO PORT PTR->ODR &= ~(1 << pin);

void togglePin(GPIO_TypeDef* GPIO_PORT_PTR,int pin) {

GPIO PORT PTR->ODR ^= (1 << pin);

```

### STM32F401RE\_I2C.h

```

#ifndef STM32F4 I2C H

#define STM32F4 I2C H

#include <stdint.h>

\#define I2C1 BASE (0x40005400UL)

volatile uint32 t PE

: 1;

volatile uint32 t SMBUS

: 1;

: 1;

volatile uint32 t SMBTYPE

: 1;

volatile uint32 t ENPEC

: 1;

volatile uint32 t ENGC : 1;

volatile uint32 t NO STRETCH : 1;

volatile uint32 t START : 1;

volatile uint32 t STOP

: 1;

volatile uint32 t ACK

: 1;

volatile uint32 t POS

volatile uint32 t PEC

volatile uint32 t ALERT : 1;

```

```

volatile uint32 t SWRST

: 1;

} I2C CR1 bits;

typedef struct {

volatile uint32 t FREQ : 6;

: 2;

volatile uint32 t ITERREN : 1;

volatile uint32 t ITEVTEN : 1;

volatile uint32 t ITBUFEN : 1;

volatile uint32 t DMAEN : 1;

volatile uint32 t

typedef struct {

volatile uint32 t reserved2 : 1;

volatile uint32 t ADDMODE : 1;

volatile uint32 t : 16;

typedef struct {

: 1;

volatile uint32 t ADDR

: 1;

```

```

: 1;

: 1;

volatile uint32 t OVR

volatile uint32 t PEC ERR : 1;

volatile uint32 t SMB ALERT : 1;

: 16;

volatile uint32 t MSL

: 1;

volatile uint32 t BUSY

: 1;

volatile uint32 t TRA

: 1;

: 1;

volatile uint32 t GENCALL

: 1;

volatile uint32 t SMBHOST : 1;

volatile uint32_t DUALF : 1;

volatile uint32 t PEC

: 16;

typedef struct {

volatile uint32 t DUTY

: 1;

volatile uint32 t FS

: 16;

} I2C CCR bits;

typedef struct {

Address offset: 0x00 */

CR2;

Address offset: 0x04 */

Address offset: 0x08 */

```

```

OAR2;

Address offset: 0x0C */

Address offset: 0x10 */

SR1;

Address offset: 0x14 */

SR2;

Address offset: 0x18 */

CCR:

Address offset: 0x1C */

TRISE;

Address offset: 0x20 */

FLTR;

Address offset: 0x24 */

I2C TypeDef;

#define I2C1 ((I2C TypeDef *) I2C1 BASE)

void configureI2C(void);

void enable I2C(void);

void disable I2C(void);

void I2C write to DAC(uint8 t address, uint16 t msg);

void I2C fast write to DAC(uint8 t address, uint16 t msg);

void I2C general call reset(void);

void I2C start and send address(uint8 t address);

#endif

```

#### STM32F401RE I2C.c

```

// STM32F401RE_GPIO.c

// Source code for I2C functions

#include "STM32F401RE_I2C.h"

#include "STM32F401RE_RCC.h"

```

```

uint8 t DAC WRITE COMMAND = 0b01000000;

void configureI2C(void) {

RCC->APB1ENR \mid = (1<<21);

I2C1->CR1.PE = 0;

I2C1->CR1.SMBUS = 0;

I2C1->OAR1.ADDMODE = 0;

I2C1->OAR1.reserved2 = 1;

I2C1->CCR.FS = 1;

I2C1->CCR.DUTY = 1;

I2C1->CR2.FREO = 42;

I2C1 -> CCR.CCR = 4;

I2C1->TRISE = 13;

void enable I2C(void) {

I2C1->CR1.PE = 1;

```

```

void disable I2C(void) {

I2C1->CR1.PE = 0;

I2C1->CR1.START = 1;

while (I2C1->SR1.SB != 1);

address |= 0;

I2C1->DR.DR = address;

while (I2C1->SR1.ADDR != 1);

while (I2C1->SR2.MSL != 1);

void I2C general call reset(void) {

I2C start and send address(0x00); // general call

I2C1->DR.DR = 0 \times 06; // general call reset code

while (I2C1->SR1.TxE != 1);

I2C1->CR1.STOP = 1;

void I2C fast write to DAC(uint8 t address, uint16 t msg) {

```

```

I2C_start_and_send_address(address);

// send first eight bits of the message

I2C1->DR.DR = (uint8_t) (msg >> 8);

// wait for transmission to be successful

while (I2C1->SR1.TxE != 1);

// send last eight bits of the message

I2C1->DR.DR = (uint8_t) (msg);

// wait for transmission to be successful

while (I2C1->SR1.TxE != 1);

// send STOP byte

I2C1->CR1.STOP = 1;

}

```

# STM32F401RE\_RCC.h

```

STM32F401RE_RCC.h

// STM32F401RE_RCC.h

// Header for RCC functions

#ifndef STM32F4_RCC_H

#define STM32F4_RCC_H

#include <stdint.h>

//////

// Definitions

//////

////

#define __IO volatile

// Base addresses

#define RCC_BASE (0x40023800UL) // base address of RCC

// PLL

#define PLLSRC_HSI 0

```

```

#define PLLSRC HSE 1

// Clock configuration

#define SW HSI 0

#define SW HSE 1

#define SW PLL 2

// fastest clock speed

uint32 t SystemCoreClock; // Updated by configureClock()

volatile uint32 t HSION

: 1;

volatile uint32 t HSIRDY

: 1;

volatile uint32 t HSITRIM : 5;

: 1;

volatile uint32 t HSERDY : 1;

volatile uint32 t HSEBYP

: 1;

volatile uint32 t CSSON : 1;

volatile uint32 t PLLRDY : 1;

volatile uint32 t PLLI2SON : 1;

volatile uint32 t PLLI2SRDY : 1;

volatile uint32 t

volatile uint32 t PLLM

: 1;

```

```

volatile uint32 t PLLQ

typedef struct {

: 2;

volatile uint32 t HPRE

: 2;

volatile uint32 t PPRE1

volatile uint32 t PPRE2

volatile uint32 t RTCPRE

volatile uint32 t MCO1

: 2;

volatile uint32 t I2SSCR

: 1;

volatile uint32 t MCO1PRE : 3;

volatile uint32 t MCO2PRE : 3;

volatile uint32 t MCO2 : 2;

volatile uint32 t GPIOAEN : 1;

volatile uint32 t GPIOBEN : 1;

volatile uint32 t GPIOCEN : 1;

volatile uint32 t GPIODEN : 1;

volatile uint32 t GPIOEEN : 1;

volatile uint32 t GPIOHEN : 1;

volatile uint32 t CRCEN

: 1;

volatile uint32 t

volatile uint32 t DMA1EN

: 1;

```

```

IO PLLCFGR bits PLLCFGR;

Address offset: 0x04 */

Address offset: 0x08 */

Address offset: 0x0C */

IO uint32 t AHB1RSTR; /*!< RCC AHB1 peripheral reset register,

Address offset: 0x10 */

IO uint32 t AHB2RSTR;

Address offset: 0x14 */

IO uint32 t AHB3RSTR; /*! < RCC AHB3 peripheral reset register,

Address offset: 0x18 */

uint32 t

RESERVEDO;

IO uint32 t APB1RSTR;

Address offset: 0x20 */

IO uint32 t APB2RSTR;

Address offset: 0x24 */

RESERVED1[2]; /*! Reserved, 0x28-0x2C

Address offset: 0x30 */

Address offset: 0x34 */

IO uint32 t AHB3ENR;

Address offset: 0x38 */

RESERVED2; /*!< Reserved, 0x3C

* /

register,

register,

uint32 t RESERVED3[2]; /*! < Reserved, 0x48-0x4C

low power mode register, Address offset: 0x50 */

low power mode register, Address offset: 0x54 */

IO uint32 t AHB3LPENR; /*!< RCC AHB3 peripheral clock enable in

```

```

RESERVED4; /*!< Reserved, 0x5C

low power mode register, Address offset: 0x60 */

APB2LPENR; /*!< RCC APB2 peripheral clock enable in

RESERVED5[2]; /*!< Reserved, 0x68-0x60

IO uint32 t BDCR;

RESERVED6[2]; /*! < Reserved, 0x78-0x7C

uint32 t

IO uint32 t SSCGR; /*! < RCC spread spectrum clock

IO uint32 t PLLI2SCFGR;

Address offset: 0x84 */

#define RCC ((RCC TypeDef *) RCC BASE)

void configurePLL();

void configureClock();

#endif

```

### STM32F401RE RCC.c

```

// STM32F401RE_RCC.c

// Source code for RCC functions

```

```

#include "STM32F401RE RCC.h"

void configurePLL() {

RCC->CR.PLLON = 0; // Turn off PLL

while (RCC->CR.PLLRDY != 0); // Wait till PLL is unlocked (e.g., off)

RCC->PLLCFGR.PLLSRC = PLLSRC HSE;

RCC->PLLCFGR.PLLM = 8;

RCC->PLLCFGR.PLLN = 336;

RCC->PLLCFGR.PLLP = 0b01;

RCC->PLLCFGR.PLLQ = 4;

RCC->CR.PLLON = 1;

while(RCC->CR.PLLRDY == 0);

void configureClock(){

RCC->CFGR.PPRE2 = 0b000;

RCC->CFGR.PPRE1 = 0b100;

RCC->CR.HSEBYP = 1;

RCC->CR.HSEON = 1;

while(!RCC->CR.HSERDY);

```

```

configurePLL();

RCC->CFGR.SW = SW PLL;

while (RCC->CFGR.SWS != 0b10);

SystemCoreClock = 84000000;

```

## STM32F401RE SPI.h

```

#ifndef STM32F4 SPI H

#define STM32F4 SPI H

#include <stdint.h> // Include stdint header

#define SPI1 BASE (0x40013000UL)

#define IO volatile

IO uint32 t CPHA

: 1;

IO uint32 t CPOL

IO uint32 t MSTR

IO uint32 t SPE

IO uint32 t LSBFIRST : 1;

```

```

__IO uint32_t SSI

typedef struct {

: 1;

: 1;

IO uint32 t SSOE

: 1;

: 24;

: 1;

IO uint32 t BSY

```

```

typedef struct {

typedef struct {

IO SPI CR1 bits CR1; /*!< SPI control register 1 (not used in

Address offset: 0x04 */

Address offset: 0x08 */

Address offset: 0x0C */

IO uint32 t CRCPR; /*! < SPI CRC polynomial register (not used in

I2S mode), Address offset: 0x10 */

mode), Address offset: 0x14 */

Address offset: 0x1C */

IO uint32 t I2SPR; /*! SPI I2S prescaler register,

Address offset: 0x20 */

} SPI TypeDef;

#define SPI1 ((SPI TypeDef *) SPI1 BASE)

^{\prime *} Enables the SPI peripheral and intializes its clock speed (baud rate),

polarity, and phase.

```

```

void spiInit(uint32 t clkdivide, uint32 t cpol, uint32 t ncpha);

character.

uint8 t spiSendReceive(uint8 t send);

uint16 t spiSendReceive16(uint16 t send);

#endif

```

#### STM32F401RE SPI.c

```

// STM32F401RE_SPI.c

// SPI function declarations

#include "STM32F401RE_SPI.h"

#include "STM32F401RE_RCC.h"

#include "STM32F401RE_GPIO.h"

```

```

polarity, and phase.

changed on next edge,

edge)

void spiInit(uint32 t br, uint32 t cpol, uint32 t cpha) {

AHB1ENR)

RCC->AHB1ENR.GPIOAEN = 1;

RCC->AHB1ENR.GPIOBEN = 1;

RCC->APB2ENR |= (1 << 12); // Turn on SPI1 clock domain (SPI1EN bit in</pre>

pinMode (GPIOA, 5, GPIO ALT); // PA5, Arduino D13, SPI1 SCK

pinMode(GPIOA, 6, GPIO ALT); // PA6, Arduino D12, SPI1 MISO

pinMode (GPIOA, 7, GPIO ALT); // PA7, Arduino D11, SPI1 MOSI

pinMode (GPIOB, 5, GPIO OUTPUT); // PB5, Arduino D10, Manual CS

GPIOA->OSPEEDR |= (0b11 << 2*5);

GPIOA->AFRL |= (1 << 18) | (1 << 16);

GPIOA->AFRL |= (1 << 22) | (1 << 20);

GPIOA->AFRL |= (1 << 26) | (1 << 24);

GPIOA->AFRL |= (1 << 30) | (1 << 28);

SPI1->CR1.BR = br; // Set the clock divisor

SPI1->CR1.CPOL = cpol; // Set the polarity

```

```

SPI1->CR1.CPHA = cpha; // Set the phase

SPI1->CR1.LSBFIRST = 0; // Set least significant bit first

SPI1->CR1.SSM = 0;

SPI1->CR1.MSTR = 1;

SPI1->CR1.SPE = 1; // Enable SPI

uint8 t spiSendReceive(uint8 t send) {

digitalWrite(GPIOB, 5, 1);

SPI1->CR1.SPE = 1;

while(!(SPI1->SR.TXE)); // Wait until the transmit buffer is empty

SPI1->DR.DR = send; // Transmit the character over SPI

while(!(SPI1->SR.RXNE)); // Wait until data has been received

uint8 t rec = SPI1->DR.DR;

SPI1->CR1.SPE = 0;

digitalWrite(GPIOB, 5, 0);

return rec; // Return received character

uint16 t spiSendReceive16(uint16 t send) {

digitalWrite(GPIOB, 6, 0);

SPI1->CR1.SPE = 1;

SPI1->DR.DR = send;

while(!(SPI1->SR.RXNE));

uint16 t rec = SPI1->DR.DR;

SPI1->CR1.SPE = 0;

digitalWrite(GPIOB, 6, 1);

```

```

return rec;

}

```

# STM32F401RE\_SYSCFG.h

```

#ifndef STM32F4 SYSCFG H

#define STM32F4 SYSCFG H

#include <stdint.h>

#define IO volatile

#define SYSCFG BASE (0x40013800UL)

typedef struct {

IO uint32 t MEMRMP

:32;

:32;

:32;

:32;

:32;

:32;

#define SYSCFG ((SYSCFG TypeDef *) SYSCFG BASE)

void configureFlash();

```

### STM32F401RE\_TIM2\_5.h

```

#ifndef STM32F4 TIM H

#define STM32F4 TIM H

#include <stdint.h>

#define IO volatile

#define TIM2 BASE (0x40000000UL)

#define TIM3 BASE (0x40000400UL)

#define TIM4 BASE (0x40000800UL)

#define TIM5 BASE (0x40000C00UL)

typedef struct {

: 1;

: 1;

: 1;

: 1;

volatile uint32 t ARPE

volatile uint32 t SMS

```

```

volatile uint32 t ETF

volatile uint32 t ETPS

volatile uint32 t ECE

: 1;

: 1;

: 16;

volatile uint32 t OC1FE

volatile uint32 t OC1PE

: 1;

volatile uint32 t OC1M

volatile uint32 t OC1CE

: 1;

volatile uint32 t CC2S

: 2;

volatile uint32 t OC2FE

: 1;

volatile uint32 t OC2PE

: 1;

: 1;

: 16;

: 1;

: 1;

: 1;

: 1;

volatile uint32 t CC4G

: 1;

: 1;

volatile uint32 t TG

: 1;

: 25;

volatile uint32 t UIF

: 1;

volatile uint32 t CC1IF

: 1;

volatile uint32 t CC2IF

: 1;

: 1;

volatile uint32 t CC4IF

: 1;

: 1;

: 1;

```

```

: 1;

volatile uint32 t CC30F

: 1;

volatile uint32 t CC40F

: 1;

: 19;

typedef struct {

Address offset: 0x00 */

IO uint32 t CR2;

Address offset: 0x04 */

IO SMCR bits

Address offset: 0x08 */

IO uint32 t DIER;

register,

Address offset: 0x10 */

Address offset: 0x14 */

IO CCMR1 bits CCMR1;

_IO uint32 t CCMR2;

CCER;

IO uint32 t CNT;

Address offset: 0x24 */

PSC;

Address offset: 0x28 */

ARR;

Address offset: 0x2C */

Address offset: 0x34 */

Address offset: 0x38 */

```

```

CCR4;

Address offset: 0x40 */

reserved2;

DCR;

Address offset: 0x48 */

DMAR;

Address offset: 0x4C */

Address offset: 0x40 */

TIM TypeDef;

#define TIM2 ((TIM TypeDef *) TIM2 BASE)

#define TIM3 ((TIM TypeDef *) TIM3 BASE)

#define TIM4 ((TIM TypeDef *) TIM4 BASE)

#define TIM5 ((TIM TypeDef *) TIM5 BASE)

// function prototypes

void configureTimer(TIM TypeDef* TIM);

void configureShortARRTimer(TIM TypeDef* TIM);

void configureLongARRTimer(TIM TypeDef* TIM);

void setPWMTimer(TIM TypeDef* TIM, float freq);

void configureDurationTimer(TIM TypeDef* TIM);

void configureMotorTimer(TIM TypeDef* TIM);

void changePWM(TIM TypeDef* TIM, int frequency);

void changeMotorPWM(TIM TypeDef* TIM, int frequency);

void setTimerFromTime(TIM TypeDef* TIM, int time);

#endif

```

# STM32F401RE\_TIM2\_5.c

```

// STM32F401RE_TIM2_5.c

// Function declarations for timers 2 through 5

#include "STM32F401RE_TIM2_5.h"

#include "STM32F401RE_RCC.h"

#include <stdio.h>

#include <math.h>

#define FAST 0

```

```

#define SLOW 1

void configureTimer(TIM TypeDef* TIM) {

TIM->SMCR.SMS = 0b000;

TIM->CR1.CEN = 1; // enable clock

TIM->CCMR1.CC1S = 0b00; // configure OC1 as output

TIM->CCMR1.OC1PE = 1; // enable preload register

TIM->CR1.DIR = 0; // put timer in upcounting configuration

void configureDurationTimer(TIM TypeDef* TIM) {

RCC->APB1ENR |= 0b1111; // enable APB1 peripheral clock (timer

location)

RCC->CFGR.MCO1 = 3;  // Set output of MCO1 to be PLL

TIM->CCR1 = 0x006ACFC0;

TIM->ARR = 0x00D59F80;

TIM->CR1.ARPE = 1;

TIM->CCMR1.OC1M = 6;

TIM->CCER |= 1;

TIM->DIER |= (1 << 1); // Allow capture compare channel 1 to give

TIM->EGR.UG = 1;

TIM->CR1.CEN = 1;

TIM->EGR.UG = 1;

void configureMotorTimer(TIM TypeDef* TIM) {

RCC->CFGR.MCO1 = 3; // Set output of MCO1 to be PLL

TIM->CCR1 = 2;

\overline{\text{TIM->ARR}} = 3;

```

```

TIM->CCMR1.OC1PE = 1;  // enable preload register

TIM->CR1.ARPE = 1;

TIM->CCMR1.OC1M = 6;

TIM->CCER \mid = 1;

TIM->EGR.UG = 1;

TIM->CR1.CEN = 1;

TIM->EGR.UG = 1;

TIM->PSC = 1282;

void setTimerFromTime(TIM TypeDef* TIM, int time) {

1000);

setPWMTimer(TIM, slowTimerHz);

void changePWM(TIM TypeDef* TIM, int frequency) {

if (frequency == 0) {

TIM->ARR = (int) (2);

TIM->CCR1 = (int) (3);

TIM->ARR = (long) (SystemCoreClock/frequency);

TIM->CCR1 = (long) (SystemCoreClock/(2*frequency));

void changeMotorPWM(TIM TypeDef* TIM, int frequency) {

if (frequency == 0) {

TIM->ARR = (int) (2);

TIM->CCR1 = (int) (3);

TIM->ARR = (long) (SystemCoreClock/1282/frequency);

TIM->CCR1 = (long) (SystemCoreClock/1282/(2*frequency));

void configureLongARRTimer(TIM TypeDef* TIM) {

```

```

accuracy

configureTimer(TIM);

TIM->PSC = 0;

void setPWMTimer(TIM TypeDef* TIM, float freq) {

have any rounding

int clockFreq = (int) (84 * pow(10, 6))/(TIM->PSC + 1);

frequency

int valueToCountTo = (int) ((float)(clockFreq)) / (float) (freq * 2.0);

TIM->ARR = valueToCountTo;

of the TIMx ARR

is set to use OC1

TIM->CCR1 = valueToCountTo/2;

register

TIM->EGR.UG = 1;

```

### STM32F401RE TIM10 11.h

```

// STM32F401RE_TIM10_11.h

// Header for timer functions, for timers 10 through 11

```

```

#ifndef STM32F4 TIM10 11 H

#define STM32F4 TIM10 11 H

#include <stdint.h>

#define IO volatile

#define TIM10 BASE (0x40014400UL)

#define TIM11 BASE (0x40014800UL)

typedef struct {

: 1;

volatile uint32 t OPM

volatile uint32 t ARPE

volatile uint32 t CC1S : 2;

volatile uint32 t OC1FE

: 1;

volatile uint32 t OC1PE

: 1;

volatile uint32 t OC1M

: 2;

volatile uint32 t OC2PE

volatile uint32 t OC2CE

: 1;

: 16;

CCMR1;

```

```

typedef struct {

: 30;

typedef struct {

volatile uint32 t UIF : 1;

volatile uint32 t CC1IF

: 1;

volatile uint32 t CC10F

: 1;

: 22;

typedef struct {

Address offset: 0x00 */

SMCR;

Address offset: 0x08 */

Address offset: 0x0C */

Address offset: 0x10 */

Address offset: 0x14 */

IO CCMR1 CCMR1;

Address offset: 0x18 */

IO uint32 t CCER;

Address offset: 0x20 */

Address offset: 0x24 */

PSC;

Address offset: 0x28 */

Address offset: 0x2C */

IO uint32 t reserved1;

```

### STM32F401RE TIM10 11.c

```

// STM32F401RE_TIM10_11.c

// Function declarations for timers 10 through 11

#include "STM32F401RE_TIM10_11.h"

#include <stdio.h>

#include <math.h>

void configureTimer1011(TIM1011_TypeDef* TIM) {

// the clock will be sent to CK_INT by default

// since we only have one PWM timer, we can assume that it just uses

OC1

// configure OC1 as output

TIM->CCMR1.CC1S = 0b00;

```

```

TIM->CCMR1.OC1M = 0b110;

TIMx CCMRx register

TIM->CCMR1.OC1PE = 1;

TIM->CR1.ARPE = 1;

void setTimerFromFreq1011(TIM1011 TypeDef* TIM, float freq) {

factor

have any rounding

int clockFreq = (int) (84 * pow(10, 6))/(TIM->PSC + 1);

frequency

int valueToCountTo = (int) ((float)(clockFreq)) / (float) (freq * 2.0);

generate the right frequency

TIM->ARR = valueToCountTo;

TIM->CCR1 = valueToCountTo/2;

TIM->EGR.UG = 1;

```

```

// set CEN bit in TIMx_CR1 to 1 to enable the clock

TIM->CR1.CEN = 1;

}

```

## Appendix B: Verilog code

```

System Verilog code for MC You

Takes input from a 4x3 matric keypad and two pushbutton switches

Interprets them as user commands, records and saves timing information,

and sends it over an SPI link

Author: Kariessa Schultz

Email: kschultz@g.hmc.edu

Created 12/8/2021

*/

/*

Pin assignments

PIN_H6: clk, 12MHz clock

PIN H4: sck, for SPI

PIN_H1: MISO/sdo, for SPI

PIN J1: MOSI/sdi, for SPI

PIN J13: CS, for SPI

PIN_H5: ready, signals MCU when there is data to be read from the FPGA

PIN K10: record I, input from left record pushbutton

PIN E3: record r, input from right record pushbutton

PIN_F1: row[0], controls 0th row of the keypad

PIN E4: row[1], controls 1st row of the keypad

PIN H8: row[2], controls 2nd row of the keypad

PIN H13: row[3], controls the 3rd row of the keypad

PIN_E1: col[0], 0th column of the keypad

PIN_C2: col[1], 1st column of the keypad

PIN_C1: col[2], 2nd column of the keypad

*/

mcyou

Top level module with SPI interface and input processor core

Author: Kariessa Schultz

Email: kschultz@g.hmc.edu

Created 12/4/2021

*/

module mcyou(

```

```

input logic clk,

input logic sck, sdi, cs,

input logic recordl, recordr,

input logic [2:0] col,

output logic [3:0] row,

output logic sdo,

output logic ready,

output logic [7:0] led

);

logic [3:0] clean input;

logic [647: 0] memory = 0;

spi spi(sck, sdi, sdo, cs, memory);

processorCore core(clk, cs, row, col, clean input, ready, memory, recordl, recordr, led);

endmodule

spi

SPI interface. Shifts out contents of memory module.

Assumes that the data on sdi will always take the form 0x8000...0

Author: Kariessa Schultz

Email: kschultz@g.hmc.edu

Created 12/6/2021

*/

module spi(

input logic sck, sdi,

output logic sdo,

input logic cs,

input [647:0] memory

);

logic sdodelayed = 0;

logic [647:0] memorycaptured = 0; // shift register

// shift the register one bit at a time on the positive edge of sck

always ff @(posedge sck) begin

if (sdi == 1) memorycaptured = memory;

// initialize shift register with the input

else {memorycaptured} = {memorycaptured[646:0], sdi};

end

// sdo should change on the negative edge of sck

always ff @(negedge sck) begin

```

```

sdodelayed = memorycaptured[646];

end

// when the MCU sends the first sdi signal, shift out msb before clock edge

// by definition, the msb is always 0

assign sdo = (sdi == 1) ? 0 : sdodelayed;

endmodule

processorCore

High level module: wires together other modules for reading and storing user input

Author: Kariessa Schultz

Email: kschultz@g.hmc.edu

Created 12/8/2021

module processorCore(

input logic clk, cs,

output logic [3:0] row,

input logic [2:0] col,

output logic [3:0] clean_key_input,

output logic ready,

output logic [647:0] memory,

input logic recordl, recordr,

);

logic [11:0] one hot;

logic [3:0] raw_key_input;

logic en, newCommand, recordPressed, clean_record_r_input, clean_record_l_input;

logic saveBeat, saveTime, saveCommand, clearCommand, recordCommand;

logic [31:0] stopwatch;

logic [3:0] regPointer;

assign recordPressed = clean_record_r_input | clean_record_l_input;

// read and debounce user input and save it in a register for later processing

keypadScanner scanner(clk, col, row, one hot);

switchDebouncer keypadBouncer (clk, raw_key_input, en, newCommand, recordCommand);

recordDebouncer recordBouncerr (clk, recordr, clean record r input);

recordDebouncer recordBouncerl (clk, recordl, clean record I input);

// translate input into a four bit internal representation

decoder decoder(one hot, raw key input);

```

commandRegister commandr(clk, en, raw\_key\_input, clean\_key\_input);

```

commander com(

clk,

newCommand,

recordCommand,

CS,

recordPressed,

ready,

saveBeat,

saveTime.

saveCommand,

clearCommand,

stopwatch,

regPointer

);

recordMemory mem(

clk,

saveBeat.

saveTime,

saveCommand.

clearCommand,

clean_key_input,

clean_record_l_input,

clean_record_r_input,

stopwatch,

regPointer,

memory

);

endmodule

keypadScanner

```

This module reads the input from the 4x3 matrix keypad by sending voltage to each row in turn, and recording the result as a one-hot encoding. The one-hot encoding is twelve bits; each three bit segment represents the result of sending the voltage to a different row.

Adapted from code written by Kariessa Schultz for a 4x4 matrix keypad in lab 4 (9/26/2021)

```

Author: Kariessa Schultz

Email: kschultz@g.hmc.edu

Created 11/28/2021

module keypadScanner(

input logic clk,

input logic [2:0] col,

output logic [3:0] row,

output logic [11:0] one hot

);

logic [7:0] clk counter = 8'h00;

always_ff@(posedge clk) begin

clk counter = clk counter > 8'hF0 ? 8'h00 : clk counter + 1;

if ((clk counter >= 0)

&& (clk_counter < 8'h3C)) begin

// row 0 (keys 1, 2, 3)

row = 4'b0001;

one_hot[11:9] = col;

end else if ((clk counter >= 8'h3C)

&& (clk counter < 8'h7A)) begin // row 1 (keys 4, 5, 6)

row = 4'b0010;

one hot[8:6] = col;

end else if ((clk counter >= 8'h7A)

&& (clk_counter < 8'hB4)) begin // row 2 (keys 7, 8, 9)

row = 4'b0100;

one_hot[5:3] = col;

end else begin

// row 3 (keys *, 0, #)

row = 4'b1000;

one_hot[2:0] = col;

end

end

endmodule

decoder

```

This module decodes clean user input into the commands to be sent to the FPGA

It assumes that user input is a one-hot encoding, so if multiple keys are pressed, it will only register the 'first' one as the input

It is not responsible for handling the recording buttons, but the encoded commands from the beat keys can be sent to the MCU as they are, and will be interpreted as

#### commands to play the correct beats

```

Author: Kariessa Schultz

Email: kschultz@g.hmc.edu

Created 12/7/2021

*/

module decoder(

input logic [11:0] one hot,

output logic [3:0] command

);

always comb

casez(one hot)

12'b1????????? command = 4'h3; // key 3: record beat 3

12'b01????????: command = 4'h2; // key 2: record beat 2

12'b001????????: command = 4'h1; // key 1: record beat 1

12'b0001???????: command = 4'hD; // key 6: pause or resume motor song

12'b00001??????: command = 4'h8; // key 5: play sequence 2 once

12'b000001??????: command = 4'h7; // key 4: play sequence 1 once

12'b0000001?????: command = 4'h4; // key 9: play motor song from beginning

12'b00000001????: command = 4'hA; // key 8: play sequence 2 on repeat

12'b00000001???: command = 4'h9; // key 7: play sequence 1 on repeat

12'b000000001??: command = 4'h0; // key #: no meaning assigned...

12'b0000000001?: command = 4'hB; // key 0: go back to marked spot in motor song

12'b00000000001: command = 4'hC; // key *: mark spot in motor song

12'b00000000000: command = 4'h0; // no meaning assigned...

default

: command = 4'h0; // no meaning assigned...

endcase

endmodule

switchDebouncer

```

This module deals with switch bounce for the keypad input.

It waits between 10 and 20 ms after first detecting a change in input to do anything about it. The value is between 10 and 20 ms, because it waits for a clock counter to equal zero, and then for it to equal its max value, which takes at least 10 ms and up to 20 ms.

After waiting between 10 and 20 ms, if the change in input persists, then the module saves the input in a register for other modules to handle

It then asserts newCommand to tell the commander it saw new input, and asserts recordCommand if the key that was pressed was '1', '2', or '3'

Once the user is no longer pressing a key, it resets in preparation to handle the next input

```

Author: Kariessa Schultz

Email: kschultz@g.hmc.edu

Created 12/7/2021

*/

module switchDebouncer(

input logic clk,

input logic [3:0] raw_input,

output logic en, newCommand, recordCommand

);

typedef enum logic [2:0] {S0, S1, S2, S3, S4, S5, S6, S7} statetype;

statetype state = S0;

statetype nextState = S0;

logic [16:0] clk counter = 0;

always_ff@(posedge clk) begin

state <= nextState;

clk_counter <= clk_counter > 17'b11101010011000000 ? 0 : clk_counter + 1;

end

always comb

case(state)

S0: if (raw_input != 0) nextState = S1; // we saw something nonzero

else nextState = S0;

S1: if (clk_counter == 8'h00) nextState = S2; // wait for the counter edge

else nextState = S1;

S2: if (clk counter > 17'b11101010011000000)

if (raw input != 0) nextState = S3; // definitely got some input

else nextState = S0;

// false alarm, no input

else nextState = S2;

// keep waiting

S3: nextState = S7:

// clobber register with new input

S7: nextState = S4;

// signal commander

S4: if (raw input == 0) nextState = S5;

// we saw something zero

else nextState = S4;

S5: if (clk_counter == 0) nextState = S6;

// wait for the counter edge

else nextState = S5;

S6: if (clk_counter > 17'b11101010011000000)

```

This module deals with switch bounce for the record button inputs.

Based on observation from the oscilloscope, these buttons are not as prone to experiencing switch bounce. Therefore, we can switch states more quickly.

This module waits after detecting a change in input to do anything about it. After waiting, if the change in input persists, then the module assumes that the change in input is real, and heads to a different state to wait for the next change.

Because the system is only interested in whether or not the record button is currently pressed, this module does not control any registers.

Adapter from similar code written by Santiago Rodriguez for a 4x4 matrix keypad in lab 4 (9/26/2021)

```

Author: Kariessa Schultz & Santiago Rodriguez

Email: kschultz@g.hmc.edu & sdrodriguez@g.hmc.edu

Created 12/6/2021

*/

module recordDebouncer(

input logic clk,

input logic record_raw_input,

output logic record_clean_input

);

```

```

typedef enum logic [2:0] {S0, S1, S2, S3, S4, S5} statetype;

statetype state = S0:

statetype nextState = S0;

logic [4:0] clk_counter = 0;

always ff@(posedge clk) begin

if (clk counter > 5'b11100) begin

clk counter <= 0;

state <= nextState:

end else clk counter <= clk counter + 1;

end

always_comb

case(state)

S0: nextState = record_raw_input ? S1 : S0; // wait until we see something nonzero

S1: nextState = S2:

// wait for counter edge

S2: nextState = record raw input ? S3 : S0;

// confirm we saw something

nonzero

S3: nextState = record raw input ? S3 : S4;

// wait until we see something zero

S4: nextState = S5:

// wait for counter edge

S5: nextState = record_raw_input ? S3 : S0;

// confirm we saw something zero

default: nextState = S0;

endcase

// output logic

// assume we have input once we pass the debouncing test,

// then keep assuming we have input until proven otherwise

// this prevents momentary errors from messing with the commander

assign record_clean_input = ((state == S3) | (state == S4) | (state == S5));

endmodule

commander

```

This module detects when there is a new command, processes it, and asserts the ready signal when there is something new for the MCU to read

To record beats, the module stays in a recording state until the next button is pressed, incrementing a stopwatch counter.

To save user input when recording, this module increments a pointer after each beat is pressed. The pointer's value is used by the recordMemory module to save user input in the appropriate registers. We need 16 total

register pointer values, so we can use a four bit counter and let it overflow.

For any recording states where the commander might stay there a long time, there is a check to make sure that a recording button is still pressed. This ensures that the stopwatch times are accurate

cs is the chip select signal, which tells us when the command has been shifted out and we can stop asserting ready.

```

Author: Kariessa Schultz

Email: kschultz@g.hmc.edu

Created 12/7/2021

*/

module commander(

input logic clk, newCommand, recordCommand, cs, recordPressed,

output logic ready, saveBeat, saveTime, saveCommand, clearCommand,

output logic [31:0] stopwatch,

output logic [3:0] regPointer

typedef enum logic [4:0] {S0, S1, S2, S3, S33, S4, S5, S6, S7, S8, S9, S10, S11, S12}

statetype;

statetype state = S0;

statetype nextState = S0;

// go to the next state and, if needed, update stopwatch and register pointer

always ff@(posedge clk) begin

state <= nextState:

if (state == S5)

stopwatch <= 0;

else if (state == S6)

stopwatch <= stopwatch + 1;

if (state == S2)

regPointer <= 0;

else if ((state == S12) | (state == S9) | (state == S10))

regPointer <= regPointer + 1;

end

always_comb

case(state)

// states for handling keypad user commands

S0: if (recordPressed) nextState = S33;

else nextState = newCommand ? S11 : S0;

```

```

S11: nextState = S1:

// save command in memory

S1: nextState = cs ? S2 : S1; // wait for chip select to be asserted

S2: nextState = cs ? S2 : S0; // wait for chip select to be deasserted

// states for handling recording

S33: nextState = S3:

// save record command

S3: if (recordPressed) nextState = recordCommand ? S4 : S3;

else nextState = S0;

S4: nextState = S5:

// save beat

S5: nextState = S6;

// initialize stopwatch

to 0

// count time until next button pressed

S6: if (recordPressed)

nextState = recordCommand ? S7 : S6;

else nextState = S8;

// done recording

S7: nextState = S12:

// save stopwatch value

S12: nextState = S4;

// increment register pointer

S8: nextState = S9;

// save current time

S9: nextState = (regPointer == 15) ? S1 : S10;

// recording state to clear the rest of the registers, if necessary

S10: nextState = (regPointer == 15) ? S1 : S10;

default: nextState = S0;

endcase

// output logic

assign ready = (state == S1);

assign saveBeat = ((state == S4) | (state == S10));

assign saveTime = ((state == S7) | (state == S8) | (state == S10));

assign saveCommand = ((state == S33) | (state == S11));

assign clearCommand = (state == S10);

endmodule

commandRegister

A 4 bit enabled register, for storing keypad input

Author: Kariessa Schultz

Email: kschultz@g.hmc.edu

Created 12/4/2021

*/

module commandRegister(

```

```

input logic clk, en,

input logic [3:0] d,

output logic [3:0] q

);

always_ff@(posedge clk) begin

if (en) q \le d;

end

endmodule

commandRegister

A 32 bit enabled register, for storing stopwatch values

Author: Kariessa Schultz

Email: kschultz@g.hmc.edu

Created 12/6/2021

*/

module stopwatchRegister(

input logic clk, en,

input logic [31:0] d,

output logic [31:0] q

);

always_ff@(posedge clk) begin

if (en) q \le d;

end

endmodule

recordMemory

```

This module is 648 bits of registers.

The first eight bits contains the command to be sent to the FPGA, which may not be the same as the four bit internal representation of which key on the keypad has been pressed.

The next 640 bits are grouped into enabled register pairs. Each pair consists of a commandRegister and a stopwatchRegister. The command register saves {4'b0000, beat}, where beat is four bits representing which beat has been pressed. If the register does not hold a value, then beat is set to 0xF. This allows us to

record beat sequences of any length, up to the maximum of 16 beats. The stopwatch register is four bytes, and saves the time to rest after playing that beat, measured in FPGA clock cycles (12 MHz)

The register pairs are enabled and disabled based on the value of regPointer, such that only one register pair is enabled at a time.

```

Author: Kariessa Schultz

Email: kschultz@g.hmc.edu

Created 12/6/2021

*/

module recordMemory(

input logic clk, saveBeat, saveTime, saveCommand, clearCommand,

input logic [3:0] command.

input logic record_l_input, record_r_input,

input logic [31:0] stopwatch,

input logic [3:0] regPointer,

output logic [647:0] memory

);

logic [15:0] enBeat = 0;

logic [15:0] enTime = 0;

logic [3:0] commandToSave;

assign commandToSave = clearCommand ? 4'hF : command;

// write the command to the first register if the record button is

// not pressed. Otherwise, use the command that means "record left"

// or "record right" to the MCU

always ff @(posedge clk) begin

if (saveCommand)

if (record_r_input) memory[647:640] <= 8'h05;

else begin

if (record 1 input) memory [647:640] \le 8'h06;

else memory[647:640] <= {4'b0000, command};

end

end

assign enBeat = saveBeat ? (16'h0001 << regPointer) : 0;

assign enTime = saveTime ? (16'h0001 << regPointer) : 0;

oneBeatTime obt0(clk, enBeat[0], enTime[0], commandToSave, stopwatch, memory[635:632],

memory[631:600]);

```

```

oneBeatTime obt1(clk, enBeat[1], enTime[1], commandToSave, stopwatch, memory[595:592],

memory[591: 560]);

oneBeatTime obt2(clk, enBeat[2], enTime[2], commandToSave, stopwatch, memory[555:552],

memory[551: 520]);

oneBeatTime obt3(clk, enBeat[3], enTime[3], commandToSave, stopwatch, memory[515:512],

memory[511: 480]);

oneBeatTime obt4(clk, enBeat[4], enTime[4], commandToSave, stopwatch, memory[475:472],

memory[471: 440]);

oneBeatTime obt5(clk, enBeat[5], enTime[5], commandToSave, stopwatch, memory[435:432],

memory[431: 400]);

oneBeatTime obt6(clk, enBeat[6], enTime[6], commandToSave, stopwatch, memory[395:392],

memory[391: 360]);

oneBeatTime obt7(clk, enBeat[7], enTime[7], commandToSave, stopwatch, memory[355:352],

memory[351: 320]);

oneBeatTime obt8(clk, enBeat[8], enTime[8], commandToSave, stopwatch, memory[315:312],

memory[311: 280]);

oneBeatTime obt9(clk, enBeat[9], enTime[9], commandToSave, stopwatch, memory[275:272],

memory[271: 240]);

oneBeatTime obt10(clk, enBeat[10], enTime[10], commandToSave, stopwatch,

memory[235:232], memory[231: 200]);

oneBeatTime obt11(clk, enBeat[11], enTime[11], commandToSave, stopwatch,

memory[195:192], memory[191: 160]);

oneBeatTime obt12(clk, enBeat[12], enTime[12], commandToSave, stopwatch,

memory[155:152], memory[151: 120]);

oneBeatTime obt13(clk, enBeat[13], enTime[13], commandToSave, stopwatch,

memory[115:112], memory[111: 80]);

oneBeatTime obt14(clk, enBeat[14], enTime[14], commandToSave, stopwatch, memory[75:72],

memory[71: 40]);

oneBeatTime obt15(clk, enBeat[15], enTime[15], commandToSave, stopwatch, memory[35:32],

memory[31: 0]);

endmodule

oneBeatTime

This module is an enabled register pair saving a single beat and its

associated time value.

Author: Kariessa Schultz

Email: kschultz@g.hmc.edu

Created 12/6/2021

```

\*/

```

module oneBeatTime(

input logic clk, enBeat, enTime,

input logic [3:0] command_in,

input logic [31:0] stopwatch_in,

output logic [3:0] command_out,

output logic [31:0] time_out

);

commandRegister com(clk, enBeat, command_in, command_out);

stopwatchRegister tim(clk, enTime, stopwatch_in, time_out);

endmodule

```

## Appendix C: Python code

For convenience, we wrote a Python script which converts three inputted .wav files into a C header file, with audio data in the correct format for our program. This makes it easy to generate arrays of audio data for our speaker to play. See below.

```

wav converter.py

# script for reading a way file and printing it to a text file as an array of integers

# and constants, in a format consistent with C syntax

import argparse

import sys

import wave

FILE1 = "./wav files for testing/taps.wav"

FILE2 = "./wav files for testing/sine.wav"

FILE3 = "./wav files for testing/woop.wav"

OUTPUT_FILE = "audio_ data.h"

def print to file(audio file, output fp, file number):

fp1 = wave.open(audio_file, 'rb')

n frames = fp1.getnframes()

waves = fp1.readframes(n frames) # bytes object

sampwidth = fp1.getsampwidth()

framerate = fp1.getframerate()

fp1.close()

output fp.write("\n")

output_fp.write(f"int sampwidth{file_number} = {sampwidth};\n")

output fp.write(f"int framerate{file number} = {framerate};\n")

if sampwidth == 1:

output_fp.write(f"uint8_t notes{file_number}[] =")

output fp.write("{")

print("Wave file must have a bit depth of 8 (1 byte). Exiting without writing audio data.")

return

for i in range(0, len(waves) - sampwidth, sampwidth):

output_fp.write(f"{int.from_bytes(waves[i:i+sampwidth], sys.byteorder, signed=False)},")

output fp.write(f"{int.from bytes(waves[-sampwidth:], sys.byteorder, signed=False)}")

output_fp.write("};\n")

```

```

output_fp.write("\n")

def main():

with open(OUTPUT_FILE, 'w') as fp:

fp.write("// C file generated by Python script to hold audio data\n\n")

fp.write("#include <stdint.h>\n")

fp.write("#ifndef AUDIO_DATA\n")

fp.write("#define AUDIO_DATA\n")

print_to_file(FILE1, fp, 1)

print_to_file(FILE2, fp, 2)

print_to_file(FILE3, fp, 3)

fp.write("\n")

fp.write("\n")

fp.write("#endif\n")

if __name__ == "__main__":

main()

```

## Appendix D: Audio data

Here is the stepper song audio data. The speaker audio data is very long, so we have not included it here. We have included the Python script that we used to generate the header file above, so that way you may make your own arrays of audio data for the speaker if you wish.

```

const int song[] = \{0,

0,

```

```

0,

0,

440,

440,

440,

440,

440,

440,

349.2,

349.2,

392,

392,

392,

392,

392,

392,

392,

392,

392,

392,

392,

392,

392,

392,