# Musical Hat

Final Project Report December 13, 2021 E155

Mason Wray and Robert Gallardo

# Abstract

Our team attempted to create a "Musical Hat". This hat had a strip of 60 addressable LEDs fixed to the top. A microphone on the hat would take in audio data from the environment and the LED's would flash according to the audio's spectrum data as determined by a 32 point fast fourier transform (FFT). While we were unable to represent the spectrum data on the LED's correctly, we were successfully able to: convert analog audio data to digital data using an analog to digital converter (ADC), establish simultaneous serial peripheral interface (SPI) communication between the LED strip and FPGA, and develop a functioning 32 point FFT implementation using an FPGA.

## 1 Introduction

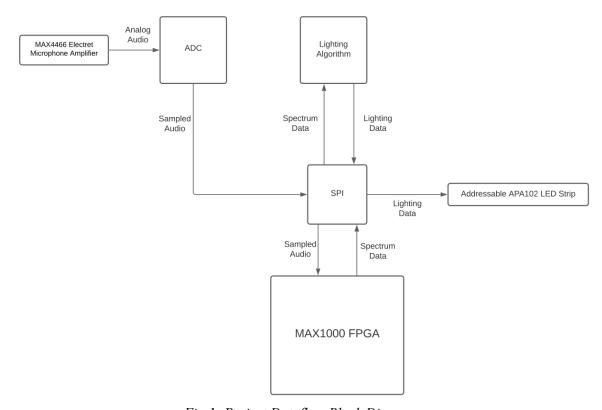

The end goal of this project was to be able to represent in real time the audio spectrum data present in the environment on a strip of 60 RGB LEDs. This would be done through sending sampled audio data to the

MAX1000 FPGA that contained an implementation of the 32 point FFT where the spectrum data would be calculated. Once the calculations were completed the FPGA would send the spectrum data back to the MCU. After receiving new spectrum data from the FPGA, the MCU would flash the LEDs on the hat depending on the frequencies present in the spectrum data. The dataflow and specifications for the project are detailed below:

- 1. Analog audio data is captured using the MAX4466 Electret Microphone Amplifier

- 2. 32 samples of audio data from the environment is sampled at a rate of 8000Hz using the Nucleo F401RE's onboard ADC. Signal duration of .125 ms.

- 3. Sampled audio data is sent to the MAX1000 FPGA using SPI communication

- 4. MAX1000 FPGA calculates the 32 point FFT on the sampled audio data

- 5. MAX1000 FPGA sends calculated spectrum data back to the MCU over SPI communication

- 6. Nucleo F401RE analyzes spectrum data and determines how the brightness of each LED on the hat needs to change.

- 7. Nucleo F401RE sends lighting data to the Addressable APA102 LED Strip over SPI communication.

- 8. Addressable APA102 LED Strip changes brightness of each LED according to lighting data.

Fig 1: Project Dataflow Block Diagram

Ultimately we were unable to flash the lights on the LED strip according to the spectrum data calculated. This was due to a communication failure when sending spectrum data back to the Nucleo F401RE (5). The following is a detailed report of the results we were able to achieve as well as a deeper discussion of the system failure that we encountered.

## 2 New Hardware

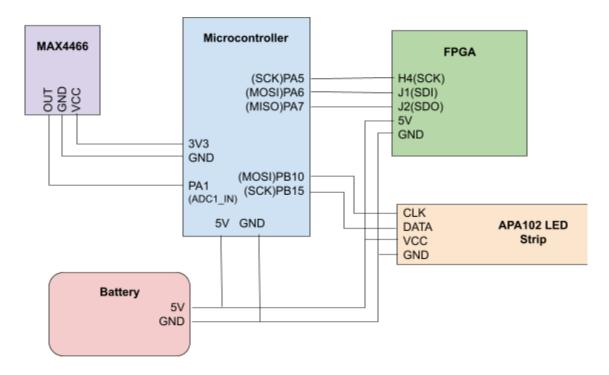

To make the musical hat, we used two new pieces of hardware: a microphone to receive analog audio data, and an individually addressable strip of 60 LEDs.

## 2.1 Electret Microphone Amplifier MAX4466

Fig 2: Image of microphone amplifier board

The microphone we used is the Electret Microphone Amplifier MAX4466. It contains a 20-20KHz electret microphone soldered to a board containing a Maxim MAX4466 op-amp with adjustable gain. The mic has three ports: VCC, GND, and OUT. We powered the mic by connecting VCC and GND to the 3.3V supply and GND on the Nucleo-64, respectively.

To read data from the mic, we connected the OUT port to pin PA1 on the MCU, which read in the analog data to the board's ADC. The MAX4466 continuously outputs audio waveform data in the form of voltage corresponding to air pressure. The output voltage values generally range from 1 to 3V depending on noise level. With typical background noise in the lab, the output ranges from 2000 to 2050 mV.

## 2.2 Addressable APA102 LED Strip

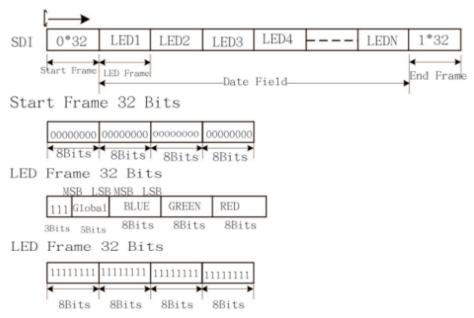

We used a one meter strip of 60 APA102 LEDs to flash with music. The strip has four input pins: Vcc, GND, CLK, and DATA. Vcc requires 5V to power the LED strip. We supplied power to the strip with a USB to pinout converter connected to a 5V portable charger. We connected the 5V pin to Vcc and the GND pin to GND.

The APA102 LEDs can be individually controlled with SPI communication using the CLK and DATA pins. We set up the SPI protocol on the MCU, connecting SCK (pin PB10) to CLK and

MOSI (pin PB15) to DATA. The communication protocol is outlined in Fig 3. As an example, to set all LEDs to red at full brightness, we first send a start frame of 32 zeros to signal to the strip, followed by 60 LED frames each with three 1s, then 'Global' set to five 1s, 'Blue' set to eight 0s, 'Green' set to eight 0s, and 'Red' set to eight 1s. Finally, we send an end frame of 32 1s to signify the transmission is complete.

Fig 3: SPI protocol for APA102 LED strip

## 3 Schematics

Fig 4: Breadboard Schematic

# 4 Microcontroller Design

The microcontroller orchestrates the overall data flow by reading from the mic using ADC, sending and receiving data from the FPGA over SPI, and sending control signals to the LED strip over SPI. This three step process is repeated continuously, with each cycle corresponding to a single 32 sample frequency and one update of the LEDs.

### **4.1 ADC**

The first step the microcontroller completes is sampling 32 data points from the mic and converting the analog voltage to a digital 16 bit value. To do so, we initialized the ADC in 'STM32F401RE\_ADC.c' with the configureADC() function. This function initializes the ADC to continuously make conversions on a single channel. Then, to sample at the desired frequency of 8kHz, we read the data stored in the ADC data register (ADC->DR.DATA) every 125 ms. We achieved this delay by initializing the MCU's built-in timer 2 (TIM2) and calling

delay\_micros(TIM2, 125). After sampling 32 times and storing each 16 bit value in an array, we then move on to sending the data to the FPGA for the FFT.

### 4.2 FPGA SPI

To send the audio waveform data to the FPGA, we used the MCU's SPI1. The FFT requires 32 points of data, each consisting of a 16 bit real part and a 16 bit imaginary part. Since the audio waveform signal consists only of real values, we simply sent 16 zeros for each imaginary part. For the real part, the ADC outputs 16 bit real values, however, these are unsigned integers and the fft requires 5 bits of overflow, meaning we can only send it values with 11 significant bits. To account for this, we divided each digital ADC output by 10 since the original values were all under 10,000 and any value under 1,000 has at most 10 significant bits. Finally, using the 16 bit SPI send/receive function 'spiSendReceive16', we sent the 32 real and imaginary data points to the FPGA to perform the FFT.

After sending the data, the MCU waits for the FPGA to assert the DONE pin, letting the MCU know the FFT has been completed and the FPGA is ready to send the data. Again using the 16 bit SPI send/receive function, the MCU reads in the 16 bit real part followed by the 16 bit imaginary part of the FFT output 32 times, corresponding to 32 frequency buckets.

## 4.3 APA102 LED Lighting

The final part of the MCUs control cycle is to update the LED strip based on the data received from the FPGA. We also designed a way to drive the LEDs using just the ADC output data in the case that the FPGA FFT data was not sufficient.

Using the FFT data, the MCU lights up the first 30 LEDs based on the amplitude of the first 30 frequencies of the discrete fourier transform (DFT) spectrum data. The updateBrightness function, in STM32F401RE\_APA102.c, sets 30 brightness levels ranging from 0 to 31 based on the amplitude of the 30 frequencies. This is calculated for the DFT real imaginary pair by taking the sum of the real part squared and the imaginary part squared and then normalizing so the max value is 31 and the min is 0.

Without using the FFT data, the MCU uses the direct ADC output data by assigning each of the first 30 LEDs and the second 30 LEDs to the first 30 samples. Similar to above, we normalize

the sample data so all the values fall between 0 and 31. If the value for sample i is greater than 15, we set LED i and LED 30+i to full brightness. If the value is less than 15, we turn that LED off. This makes the LEDs show the approximate sound wave by lighting up the upper have of the wave and turning off the lower half.

At startup, before the above three step process runs continuously, we initialize the colors of the LEDs which form a rainbow. We then run a startup sequence where the LEDs light up sequentially several times. The colors of the LEDs remain constant for the duration of the program and only their brightnesses change.

# 5 FPGA Design

When designing the FPGA logic, there were 2 main functions that the FPGA needed to perform: the 32 point FFT, and the SPI communication link with the MCU. For reference, all FPGA logic was created using the SystemVerilog code located in Appendix B.

### 5.1 32 Point FFT Design

The 32 point FFT was designed according to an implementation specified in George Slade's "The Fast Fourier Transform in Hardware: A Tutorial Based on an FPGA Implementation" [1]. This document details the implementation of a pipelined FFT using hardware. While we did not implement the pipelined version of the FFT, many of the modules remain the same or only have slight modifications that will be detailed below.

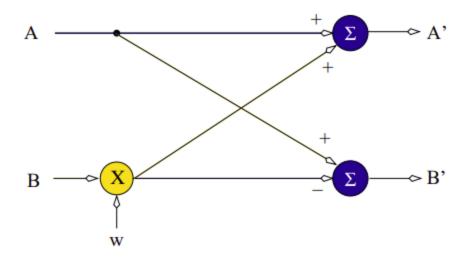

### 5.1.1 Butterfly Unit Module (BFU)

The Butterfly Unit Module is the most basic element of the FFT. It is simply a 2-point FFT on 2 complex numbers. A graphical representation of the calculation is shown below in figure 5.

Fig 5: Graphical Representation of Butterfly Unit

Here A and B are the complex inputs, w is the twiddle factor described in section 5.1.2, and A' and b' are the outputs that will be stored in memory for future calculations. In essence, for a 32 point FFT, the BFU is used over and over with different A's and B's that are specified by the AGU.

### 5.1.2 Twiddle Factor ROMs

The twiddle factors are constants that are multiplied to the B input of the Butterfly Unit Module. These twiddle factors are constant regardless of the FFT input data and depend only on the current step of the FFT being calculated. For a 32 point FFT, there are 16 twiddle factors for the real component and 16 twiddle factors for the imaginary component. The twiddle factor used is determined by the AGU. The value of the twiddle factors are determined using the following equation:

$$w^n = e^{-\frac{j2\pi n}{N}}$$

Where N is the number of points of the FFT and n is defined as N/2. The twiddle factors for a 32 point FFT were calculated in the Slade paper [1], and are shown in figure 6:

| Address $k$ | $\cos(2\pi k/32)$ | $\cos(2\pi k/32)$ | $\sin(2\pi k/32)$ | $\sin(2\pi k/32)$ |

|-------------|-------------------|-------------------|-------------------|-------------------|

|             | float             | 16-bit integer    | float             | 16-bit integer    |

| 0           | 1.0000e+00        | 0x7fff            | 0                 | 0                 |

| 1           | 9.8079e-01        | 0x7d89            | 1.9509e-01        | 0x1859            |

| 2           | 9.2388e-01        | 0x7641            | 3.8268e-01        | 0x30fb            |

| 3           | 8.3147e-01        | 0x6a6d            | 5.5557e-01        | 0x471c            |

| 4           | 7.0711e-01        | 0x5a82            | 7.0711e-01        | 0x5a82            |

| 5           | 5.5557e-01        | 0x471c            | 8.3147e-01        | 0x6a6d            |

| 6           | 3.8268e-01        | 0x30fb            | 9.2388e-01        | 0x7641            |

| 7           | 1.9509e-01        | 0x18f9            | 9.8079e-01        | 0x7d89            |

| 8           | 0                 | 0x0               | 1.0e+00           | 0x7fff            |

| 9           | -1.9509e-01       | 0xe707            | 9.8079e-01        | 0x7d89            |

| 10          | -3.8268e-01       | 0xcf05            | 9.2388e-01        | 0x7641            |

| 11          | -5.5557e-01       | 0xb8e4            | 8.3147e-01        | 0x6a6d            |

| 12          | -7.0711e-01       | 0xa57e            | 7.0711e-01        | 0x5a82            |

| 13          | -8.3147e-01       | 0x9593            | 5.5557e-01        | 0x471c            |

| 14          | -9.2388e-01       | 0x89bf            | 3.8268e-01        | 0x30fb            |

| 15          | -9.8079e-01       | 0x8277            | 1.9509e-01        | 0x1859            |

Fig 6: Table of Real & Imaginary Twiddle Factors

Because the twiddle factors are constant regardless of the input FFT data, the values for the real and imaginary twiddle factors were hardcoded into respective real and imaginary twiddle factor ROMs.

### 5.1.3 RAM Module

Due to the fact that the BFU could only compute the FFT for 2 points at a time, in order to determine a 32 point FFT we needed to create modules that continually stored the values output by the BFU so that they could be used by the BFU again later. To implement this we determined it was easiest to implement 4 separate basic RAM modules. Each module would contain either the real or imaginary components of either the A or B inputs to the BFU. Each RAM module would be controlled by the AGU individually.

### 5.1.4 Address Generation Unit (AGU)

The Address Generation Unit is the control module responsible for determining which step of the 32 point FFT calculation is to be computed, selecting the correct values from the RAMs to be calculated, and selecting the correct twiddle factors that are to be used. This module is also responsible for generating the write signals to each of the RAMs that will allow us to store the most recently computed BFU outputs. The way in which the RAM addresses and twiddle factors are generated are stated concisely in the Slade paper and is cited in figure 7:

```

/* Generate addresses for data and twiddles. */

ja = j << 1; // Multiply by 2 using left shift.

jb = ja + 1;

ja = ((ja << i) | (ja >> (5 - i))) & 0x1f; // Address A; 5 bit circular left shift

jb = ((jb << i) | (jb >> (5 - i))) & 0x1f; // Address B; implemented using C statements

TwAddr = ((0xffffffff0 >> i) & 0xf) & j; // Twiddle addresses

```

Fig 7: Generation of RAM Addresses and Twiddle Factors

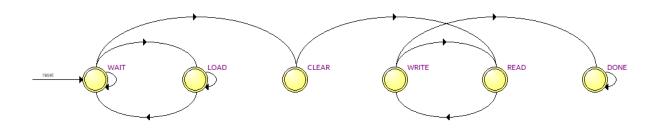

To ensure proper data flow of the FFT calculation a FSM was created. This FSM determined when write enabled for the RAMs should be asserted, began FFT calculations when data was correctly loaded in and informed the top level module when the calculation was completed. The transitions are shown in figure 8 and the next state logic is provided in appendix B.

Fig 8: Address Generation Unit FSM.

### 5.2 FPGA SPI Module

This module was responsible for collecting data to be transformed from the MCU and sending the transformed data back to the MCU. Because we were computing a 32 point FFT on 32 bit complex data the SPI module sent and received  $32 \times 32 = 1024$  bits for each FFT calculation performed.

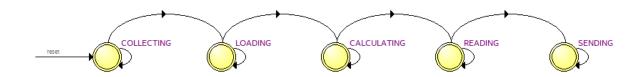

### 5.3 FPGA Top Level Control

This is the module responsible for the control of SPI communication on the FPGA, and the initiation of the FFT calculation. Additionally, this is the part of the project where the failure described in the abstract and introduction occurred. The SPI communication was designed to send 1024 bits at a time back to the MCU and the FFT outputs were designed such that only 32 bits, 1 frequency output, were output from the FFT module at each clock cycle. As a result we created an additional FSM that was responsible for counting clock cycles allowing us to have enough time to load data into the FFT, wait for the FFT calculation to begin producing outputs, and capture the correct outputs of the FFT. The next state diagram for this FSM is shown in figure 9 and the next state logic is located Appendix B:

Fig 9: Top-Level Module FSM

The problem that we encountered was during the READING state the FFT top level module was not reading the correct data from the FFT output. Instead of reading the expected FFT data, only 0s for both real and imaginary magnitudes were collected and sent back to the SPI. We believe that this was due to us not creating an elegant solution for our FSM. As mentioned above, this FSM switches states according to a number of clock cycles. We determined that it would take a variable number of clock cycles to collect data, 35 clock cycles to load data, 131 clock cycles to calculate data, and 32 clock cycles to read data. Each state of the FSM included a counter that was intended to count to each of these values in each state although there must have been an error in our determined number of clock cycles or next state logic as the values that were read from the FFT RAM's during the READING state were incorrect.

### 6 Results

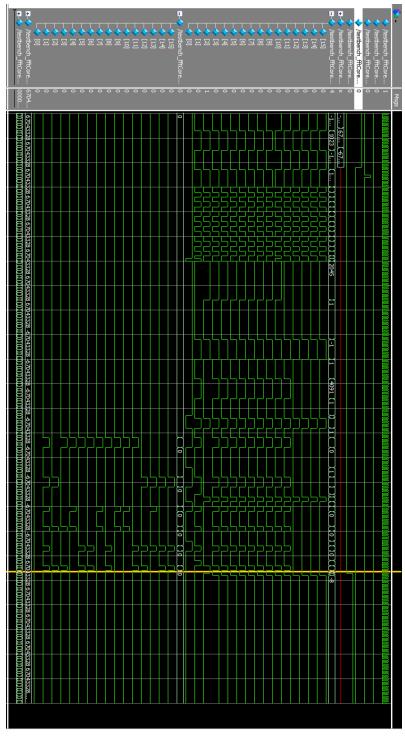

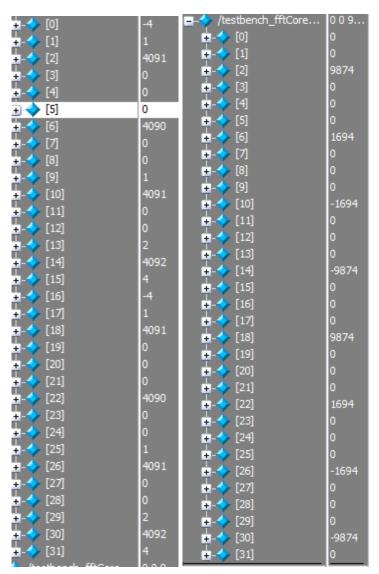

# 6.1 FFT Testbench Outputs & Stored Output Values

The waveforms and corresponding output values were calculated using the square wave described in the Slade paper [1].

Fig 10: Testbench waveforms

Fig 11: stored real & imaginary outputs

Because these values are what correspond to the FFT values of the square wave used in the slade paper, we are confident that the hardware we developed is a valid implementation of a 32 point FFT

## **Lighting Configuration**

Because the MCU was unable to receive the correct FFT output data, we used the ADC data directly as described in section 4.3 above. The hat was able to display different wavelengths corresponding to different frequencies.

# 7 References

- [1] https://web.mit.edu/6.111/www/f2017/handouts/FFTtutorial121102.pdf

- [2] http://cdn.sparkfun.com/datasheets/Components/LED/APA102C.pdf

# 8 Bill of Materials

- Microphone

- O HiLetgo 2pcs Electret Microphone Amplifier MAX4466 Module Adjustable Gain Blue Breakout Board for Arduino

- Amazon: Amazon.com: HiLetgo 2pcs Electret Microphone Amplifier

MAX4466 Module Adjustable Gain Blue Breakout Board for Arduino: Electronics

- \$8.39 for 2

- LED Strip

- Sparkfun: <a href="https://www.sparkfun.com/products/14015">https://www.sparkfun.com/products/14015</a>

- 0 \$15.95

LED RGB Strip -Addressable, 1m (APA102) © COM-14015 \$15.95

- •

- Cowboy Hat

- Amazon: <a href="https://www.amazon.com/Fun-Central-Studded-Cowboy-Western">https://www.amazon.com/Fun-Central-Studded-Cowboy-Western</a>

- 0 \$10.99

# 9 Appendices

# Appendix A: Microcontroller Code

### Main.c

```

include <stdio.h>

include "STM32F401RE.h"

#define SUCCESS LED 1 //PC

#define LOAD PIN

```

```

uint16 t testPackets[32] = {

0x03ff, 0x03ff, 0x03ff, 0x03ff, 0x03ff, 0x03ff, 0x03ff, 0x03ff,

int16 t testDfft[32][2] = {

{ (int16\ t) \ 0 \times 0001, (int16\ t) \ 0 \times 0000},

{ (int16\ t) \ 0 \times 0 \text{ffb}, (int16\ t) \ 0 \times 2692},

```

```

int main(void) {

configureFlash();

configureClock();

configureADC();

RCC->AHB1ENR.GPIOAEN = 1;

RCC->AHB1ENR.GPIOCEN = 1;

RCC->APB1ENR |= (1 << 0); // TIM2EN

initTIM(TIM2);

initSPI1(1, 0, 0); // FPGA SPI

initSPI2(1, 0, 0); // LED SPI

pinMode(GPIOB, LOAD PIN, GPIO OUTPUT);

pinMode(GPIOB, DONE PIN, GPIO INPUT);

setColorsRainbow();

updateLEDs();

startSeq(4);

```

```

uint16 t micOut = ADC->DR.DATA;

packets[i] = (uint16 t) ((float)micOut/10); // round to nearest 10

spiSendReceive16(SPI1, packets[i]); // TODO: check loop order and

spiSendReceive16(SPI1, 0x0000); // imaginary part

while(!digitalRead(GPIOB, DONE PIN));

dfftMaxVal = 0;

for (int i = 0; i < 32; i++) { // read in SPI data from FPGA

```

### ADC.h

```

// STM32F401RE_ADC.h

// Header for ADC functions

#ifndef STM32F4_ADC_H

#define STM32F4_ADC_H

#include <stdint.h>

/////

// Definitions

//////

```

```

#define IO volatile

// Base addresses for GPIO ports

#define ADC BASE (0x40012000UL) // base address of ADC

typedef struct {

:1;

:1;

:1;

IO uint32 t AWDCH : 5;

__IO uint32 t DMA

```

```

__IO uint32_t ALIGN : 1; //_O right alignment

__IO uint32_t EXTEN : 2; // Ext trigger enable for reg channels

typedef struct {

typedef struct {

typedef struct {

ADC SQR1 bits;

typedef struct {

ADC SQR3 bits;

typedef struct {

```

```

typedef struct {

__IO uint32_t ADCPRE : 2; // ADC prescaler to determine clk freq

typedef struct {

0x08 */

___IO ADC_SMPR2_bits SMPR2; /*!< ADC sample time reg 1, Address

__IO uint32_t JOFR3; /* Address offset: 0x1C */

Address offset: 0x28 */

IO ADC SQR1 bits SQR1; /*!< ADC reg seg register 1, Address

__IO uint32_t SQR2; /* Address offset: 0x30 */

__IO ADC_SQR3_bits SQR3; /*!< ADC reg seq register 1, Address

__IO uint32_t JSQR; /* Address offset: 0x38 */

__IO uint32 t JDR3;

```

### ADC.c

```

// STM32F401RE_ADC.c

// Source code for ADC functions

#include "STM32F401RE_ADC.h"

#include "STM32F401RE_RCC.h"

#include "STM32F401RE_GPIO.h"

void configureADC() {

RCC->AHB1ENR.GPIOAEN = 1; // Enable GPIOA clock domain

pinMode(GPIOA, 1, GPIO_ANALOG); // PAI, ADC1_IN1

RCC->APB2ENR |= (1 << 8); // Turn on ADC1 clock domain (ADC1EN bit in APB2ENR)

ADC->SQR1.L = Ob0000; // 1 conversion for regular channel sequence

length

ADC->SQR3.SQ1 = Ob00001; // Select channel 1 for 1st register

ADC->CR1.SCAN = 0; // Disable scan mode

ADC->CR1.RES = Ob00; // 12-bit resolution, 12+3=15 ADCCLK cycles

ADC->CR2.ALIGN = 0; // 1:left/0:RIGHT alignment

ADC->CR2.CONT = 1; // Continuous mode enabled

ADC->CR2.EXTEN = Ob00; // trigger detection disabled (Set to ... to enable)

```

```

// 11.3.1 ADC on-off control

ADC->CR2.ADON = 1; // wake up ADC from power-down mode

ADC->CR2.SWSTART = 1; // begin regular conversions

}

```

#### APA 102 h

```

#ifndef STM32F4 APA102 H

#define STM32F4 APA102 H

#include <stdint.h> // Include stdint header

#define NUM LEDS 60

#define NUM REPEATS 1 // repeat pattern twice

uint8 t colors[NUM LEDS][3]; // array of LED colors (r,g,b)

uint8 t brightness[NUM LEDS]; // array of LED brightnesses

int16 t dfft[32][2]; // output from FFT 32x(signed 16 bit real, signed 16

int16 t dfftMaxVal; // max dfft value per sample batch to normalize values

void ledFrame(uint8 t global, uint8 t r, uint8 t g, uint8 t b);

void startFrame(void);

```

```

void endFrame(void);

/* Set global 'colors' array to make LEDS rainbow */

void setColorsRainbow();

/* Update LEDs based on the brightness and colors arrays*/

void updateLEDs();

/* update 'brightness' array based on either fft output or

* direct ADC data */

void updateBrightness();

/* Sequentially brightens LEDs from first to last

* -- num: number of times to repeat sequence

* Notes: LED color is determined by values in global 'colors' array */

void startSeq(int num);

#endif

```

### APA102.c

```

// STM32F401RE_APA102.c

// Source code for APA102 LED strip functions

#include "STM32F401RE_RCC.h"

#include "STM32F401RE_GPIO.h"

#include "STM32F401RE_SPI.h"

#include "STM32F401RE_TIM.h"

#include "STM32F401RE_APA102.h"

void ledFrame(uint8_t global, uint8_t r, uint8_t g, uint8_t b) {

// combine start sequence 111 with 5 bit global (brightness)

uint8_t firstByte = (0b111 << 5) | global;

spiSendReceive(SPI2, firstByte);

spiSendReceive(SPI2, b);

spiSendReceive(SPI2, p;

}

void startFrame() {</pre>

```

```

void endFrame() {

spiSendReceive(SPI2, 0xFF);

void setColorsRainbow() {

int lenSection = NUM LEDS / NUM REPEATS;

float lenChunk = lenSection / 6; // length of each rainbow color chunk

uint8 t r = 0xFF;

for(int j = 0; j < lenSection; j++) {</pre>

float k = j % lenSection; // index within repeated sections

if (k < lenChunk) {</pre>

r = 0xFF;

g = (uint8 t) ((k / lenChunk) * 0xFF);

} else if (k \ge lenChunk & k < 2 * lenChunk) {

r = (uint8 t) (((2 * lenChunk - k) / lenChunk) * 0xFF);

q = 0xFF;

} else if (k \ge 3 * lenChunk && k < 4 * lenChunk) {

```

```

b = 0xFF;

} else if (k \ge 4 * lenChunk && k < 5 * lenChunk) {}

b = 0xFF;

} else if (k \ge 5 * lenChunk && k \le 6 * lenChunk) {

r = 0xFF;

b = (uint8 \ t) (((6 * lenChunk - k) / lenChunk) * 0xFF);

r = 0xFF;

a = 0xFF;

b = 0xFF;

colors[i*lenSection + j][0] = r;

colors[i*lenSection + j][1] = g;

colors[i*lenSection + j][2] = b;

void updateLEDs() {

startFrame();

ledFrame(brightness[i], colors[i][0], colors[i][1], colors[i][2]);

endFrame();

void updateBrightness() {

```

```

brightness[30*i+j] = (uint8 t) (((float)(dfft[j][0]-150)) *

void startSeq(int num) {

brightness[30*i+j] = (j < k) ? 0x05 : 0x01;

updateLEDs();

delay millis(TIM2, 100);

```

### SPI.h

```

// STM32F401RE_SPI.h

// Header for SPI functions

#ifndef STM32F4_SPI_H

#define STM32F4_SPI_H

```

```

#define SPI1 BASE (0x40013000UL)

#define SPI2 BASE (0x40003800UL)

#define IO volatile

IO uint32 t LSBFIRST

___IO uint32 t CRCNEXT

__IO uint32 t CRCEN

IO uint32 t BIDIOE

IO uint32 t RXDMAEN

__IO uint32_t TXDMAEN : 1;

```

```

__IO uint32 t

__IO uint32 t RXNEIE

__IO uint32_t TXEIE : 1;

typedef struct {

__IO uint32_t CRCERR : 1;

___IO uint32_t CRCNEXT : 1;

__IO uint32_t CRCEN

typedef struct {

typedef struct {

Address offset: 0x04 */

Address offset: 0x08 */

```

```

IO uint32 t CRCPR; /*! < SPI CRC polynomial register (not used in

__IO uint32 t RXCRCR;

IO uint32 t TXCRCR; /*!< SPI TX CRC register (not used in I2S

IO uint32 t I2SCFGR; /*! < SPI I2S configuration register,

IO uint32 t I2SPR;

Address offset: 0x20 */

SPI TypeDef;

#define SPI1 ((SPI TypeDef *) SPI1 BASE)

#define SPI2 ((SPI TypeDef *) SPI2 BASE)

```

```

* -- WDRBT disabled

* -- LLB disabled

* -- PCS = 0000 (Peripheral 0 selected), means NPCS[3:0] = 1110

* Refer to the datasheet for more low-level details. */

void initSPI1(uint32_t clkdivide, uint32_t cpol, uint32_t ncpha);

void initSPI2(uint32_t clkdivide, uint32_t cpol, uint32_t ncpha);

/* Transmits a character (1 byte) over SPI and returns the received character.

* -- send: the character to send over SPI

* -- return: the character received over SPI */

uint8_t spiSendReceive(SPI_TypeDef * SPIx, uint8_t send);

/* Transmits a short (2 bytes) over SPI and returns the received short.

* -- send: the short to send over SPI

* -- return: the short received over SPI */

uint16_t spiSendReceive16(SPI_TypeDef * SPIx, uint16_t send);

#endif

```

#### SPI.c

```

// STM32F401RE_SPI.c

// SPI function declarations

#include "STM32F401RE_SPI.h"

#include "STM32F401RE_RCC.h"

#include "STM32F401RE_GPIO.h"

/* Enables the SPI peripheral and intializes its clock speed (baud rate),

polarity, and phase.

* -- br: (0b000 - 0b111). The SPI clk will be the master clock /

2^(BR+1).

* -- cpol: clock polarity (0: inactive state is logical 0, 1: inactive

state is logical 1).

* -- cpha: clock phase (0: data captured on leading edge of clk and

changed on next edge,

* 1: data changed on leading edge of clk and captured on next

edge)

* Refer to the datasheet for more low-level details. */

```

```

void spiInit(SPI TypeDef * SPIx, uint32 t br, uint32 t cpol, uint32 t

cpha) {

SPIx->CR1.BR = br; // Set the clock divisor

SPIx->CR1.CPHA = cpha; // Set the phase

SPIx->CR1.LSBFIRST = 0; // Set least significant bit first

SPIx->CR2.SSOE = 1;

SPIx->CR1.SPE = 1; // Enable SPI

void initSPI1(uint32 t br, uint32 t cpol, uint32 t cpha) {

RCC->AHB1ENR.GPIOAEN = 1;

RCC->AHB1ENR.GPIOBEN = 1;

RCC->APB2ENR |= (1 << 12); // Turn on SPI1 clock domain (SPI1EN bit in

pinMode(GPIOB, 6, GPIO OUTPUT); // PB6, Arduino D10, Manual CS

GPIOA->OSPEEDR \mid = (0b11 << 2*5);

GPIOA->AFRL = (1 << 18) | (1 << 16);

GPIOA->AFRL = (1 << 22) | (1 << 20);

GPIOA->AFRL = (1 << 26) | (1 << 24);

GPIOA->AFRL = (1 << 30) | (1 << 28);

SPI1->CR1.DFF = 1; // Set data format to 16 bits

```

```

RCC->AHB1ENR.GPIOAEN = 1;

RCC->AHB1ENR.GPIOBEN = 1;

RCC->APB1ENR |= (1 << 14); // Turn on SPI1 clock domain (SPI2EN bit in

pinMode(GPIOB, 10, GPIO ALT); // PB10, Arduino D13, SPI1 SCK

GPIOB->OSPEEDR \mid= (0b11 << 2*10);

GPIOB->AFRH |= (1 << 10) | (1 << 8); // PB10 SCK

GPIOB->AFRH |= (1 << 30) | (1 << 28); // PB15 MOSI

SPI2->CR1.DFF = 0; // Set data format to 8 bits

uint8 t spiSendReceive(SPI TypeDef * SPIx, uint8 t send) {

while(!(SPIx->SR.TXE)); // Wait until the transmit buffer is empty

SPIx->DR.DR = send; // Transmit the character over SPI

while(!(SPIx->SR.RXNE)); // Wait until data has been received

uint8 t rec = SPIx->DR.DR;

return rec; // Return received character

uint16 t spiSendReceive16(SPI TypeDef * SPIx, uint16 t send) {

digitalWrite(GPIOB, 6, 0);

SPIx \rightarrow CR1.SPE = 1;

SPIx->DR.DR = send;

```

```

while(!(SPIx->SR.RXNE));

uint16_t rec = SPIx->DR.DR;

SPIx->CR1.SPE = 0;

digitalWrite(GPIOB, 6, 1);

return rec;

}

```

## Appendix B: System Verilog

### FFT Top-Level Module

```

module FinalMWRG(input logic clk, reset, sck, sdi, spiload,

output logic done, sdo);

logic [1023:0] fftinput, fftoutput;

logic [1023:0] fftDataIn, fftDataOut;

logic [5:0] ittLoad = 0; //LOAD State

logic [7:0] ittCalc = 0; //CALCULATION State

logic [31:0] wd, tempwd;

logic [15:0] outputReal, outputImag;

logic load, start;

fft spi spi(sck, sdi, sdo, done, fftinput, fftoutput);

fft_core core(clk, reset, start, load, wd, outputReal, outputImag,

done);

```

```

typedef enum logic [2:0] {COLLECTING, LOADING, CALCULATING, READING,

SENDING, NULL} statetype;

statetype currentState, nextState;

always ff @(posedge clk) begin

currentState = nextState;

if(spiload) begin

nextState = COLLECTING;

fftDataIn = fftinput;

case(currentState)

COLLECTING:

load = 0;

start = 0;

if (spiload) begin

nextState = COLLECTING;

nextState = LOADING;

LOADING:

start = 0;

```

```

nextState = LOADING;

ittLoad = ittLoad + 1;

ittLoad = 0;

nextState = CALCULATING;

CALCULATING:

load = 0;

start = 1;

if(ittCalc < 131)begin</pre>

nextState = CALCULATING;

ittCalc = ittCalc + 1;

READING:

load = 0;

start = 0;

if(ittRead < 32)begin</pre>

nextState = READING;

ittRead = 0;

```

```

SENDING:

load = 0;

start = 0;

nextState = SENDING;

NULL:

if(spiload) nextState = COLLECTING;

start = 0;

load = 0;

start = 0;

case(ittRead)

0: fftDataOut[31:0] = {outputReal, outputImag};

1: fftDataOut[63:32] = {outputReal, outputImag};

2: fftDataOut[95:64] = {outputReal, outputImag};

3: fftDataOut[127:96] = {outputReal, outputImag};

4: fftDataOut[159:128] = {outputReal, outputImag};

5: fftDataOut[191:160] = {outputReal, outputImag};

6: fftDataOut[223:192] = {outputReal, outputImag};

7: fftDataOut[255:224] = {outputReal, outputImag};

```

```

8: fftDataOut[287:256] = {outputReal, outputImag};

9: fftDataOut[319:288] = {outputReal, outputImag};

10: fftDataOut[351:320] = {outputReal, outputImag};

11: fftDataOut[383:352] = {outputReal, outputImag};

12: fftDataOut[415:384] = {outputReal, outputImag};

13: fftDataOut[447:416] = {outputReal, outputImag};

14: fftDataOut[479:448] = {outputReal, outputImag};

15: fftDataOut[511:480] = {outputReal, outputImag};

16: fftDataOut[543:512] = {outputReal, outputImag};

17: fftDataOut[575:544] = {outputReal, outputImag};

18: fftDataOut[607:576] = {outputReal, outputImag};

19: fftDataOut[639:608] = {outputReal, outputImag};

20: fftDataOut[671:640] = {outputReal, outputImag};

21: fftDataOut[703:672] = {outputReal, outputImag};

22: fftDataOut[735:704] = {outputReal, outputImag};

23: fftDataOut[767:736] = {outputReal, outputImag};

24: fftDataOut[799:768] = {outputReal, outputImag};

25: fftDataOut[831:800] = {outputReal, outputImag};

26: fftDataOut[863:832] = {outputReal, outputImag};

27: fftDataOut[895:864] = {outputReal, outputImag};

28: fftDataOut[927:896] = {outputReal, outputImag};

29: fftDataOut[959:928] = {outputReal, outputImag};

30: fftDataOut[991:960] = {outputReal, outputImag};

31: fftDataOut[1023:992] = {outputReal, outputImag};

case(ittLoad)

0: tempwd = fftinput[31:0];

1: tempwd = fftinput[63:32];

2: tempwd = fftinput[95:64];

3: tempwd = fftinput[127:96];

4: tempwd = fftinput[159:128];

5: tempwd = fftinput[191:160];

6: tempwd = fftinput[223:192];

7: tempwd = fftinput[255:224];

8: tempwd = fftinput[287:256];

9: tempwd = fftinput[319:288];

10: tempwd = fftinput[351:320];

11: tempwd = fftinput[383:352];

```

```

12: tempwd = fftinput[415:384];

13: tempwd = fftinput[447:416];

14: tempwd = fftinput[479:448];

15: tempwd = fftinput[511:480];

16: tempwd = fftinput[543:512];

17: tempwd = fftinput[575:544];

18: tempwd = fftinput[607:576];

19: tempwd = fftinput[639:608];

20: tempwd = fftinput[671:640];

21: tempwd = fftinput[703:672];

22: tempwd = fftinput[735:704];

23: tempwd = fftinput[767:736];

24: tempwd = fftinput[799:768];

25: tempwd = fftinput[831:800];

26: tempwd = fftinput[863:832];

27: tempwd = fftinput[895:864];

28: tempwd = fftinput[927:896];

29: tempwd = fftinput[959:928];

30: tempwd = fftinput[991:960];

31: tempwd = fftinput[1023:992];

default tempwd = 32'b0;

assign wd = tempwd;

assign fftoutput = fftDataOut;

```

#### FFT SPI Module

### fft\_core Module

```

clear, rdsel, k, adr0a, adr0b);

assign adrla = adr0a;

assign adr1b = adr0b;

RealTwiddles twReal(clk, k, twiddleReal);

ImagTwiddles twImag(clk, k, twiddleImag);

RAM r0r(clk, wen0, adr0a, adr0b, wda[31:16], wdb[31:16], rd0a[31:16],

rd0b[31:16]);

RAM r0i(clk, wen0, adr0a, adr0b, wda[15:0], wdb[15:0], rd0a[15:0],

rd0b[15:0]);

RAM rlr(clk, wen1, adrla, adrlb, wda[31:16], wdb[31:16], rdla[31:16],

rd1b[31:16]);

RAM r1i(clk, wen1, adr1a, adr1b, wda[15:0], wdb[15:0], rd1a[15:0],

rd1b[15:0]);

assign ain = rdsel ? rdla : rd0a;

assign bin = rdsel ? rd1b : rd0b;

ButterflyUnit bf(ain[31:16], ain[15:0], bin[31:16], bin[15:0],

twiddleReal, twiddleImag,

aout[31:16], bout[31:16], aout[15:0], bout[15:0]);

assign outputReal = ain[31:16];

assign outputImag = bin[15:0];

```

#### Address Generation Unit Module

```

output logic [4:0] addressA, addressB);

typedef enum logic [2:0] {WAIT, LOAD, READ, WRITE, CLEAR, DONE}

statetype; // Might need a clear state in between read and write

statetype currentState, nextState;

logic [5:0] counter;

always ff @(posedge clk)

if (reset) counter <= 0;</pre>

else counter <= counter + 1;</pre>

logic [4:0] j, jnext, jshift;

always ff @(posedge clk, posedge reset)

if (reset) begin

currentState <= WAIT;</pre>

end else if (clear) begin

currentState <= nextState;</pre>

currentState <= nextState;</pre>

i <= inext;</pre>

case(currentState)

```

```

else if (load) nextState <= LOAD;</pre>

else nextState <= WAIT;</pre>

LOAD: if (counter < 32) nextState <= LOAD;

nextState <= WAIT;</pre>

READ: nextState <= WRITE;</pre>

WRITE: if (i == 4 && j == 15) nextState <= DONE;

else nextState <= READ;</pre>

CLEAR:

nextState <= READ;</pre>

DONE: nextState <= DONE;</pre>

default: nextState <= WAIT;</pre>

case(currentState)

WRITE:

if(j == 15) begin

inext = i + 1;

```

WAIT: if (start) nextState <= CLEAR;</pre>

```

logic [4:0] counterRev;

bitreverse br1(counter[4:0], counterRev);

of the Slade paper

assign jshift = j << 1;

assign addressA = (currentState == LOAD) ? counterRev : ((jshift << i)</pre>

(jshift >> (5 - i))) & 8'h1f;

assign addressB = (nextState == LOAD) ? counterRev : (((jshift + 1) <<</pre>

i) | ((jshift + 1) >> (5 - i))) & 8'h1f;

assign we1 = load | ((currentState == WRITE) && memSelect);

assign we2 = ~memSelect && (currentState == WRITE);

```

```

assign done = (currentState == DONE);

assign clear = (currentState == CLEAR);

//memselect alternates in value

assign memSelect = i[0];

endmodule

```

## ButterflyUnit Module

#### Twiddle ROMs Modules

```

/*

Lookup table for the real values of the

```

```

Table was generated using the values from

Table II of the Slade Paper

inputs:

outputs:

twiddle = twiddle factor, 16 bits

module RealTwiddles (input logic clk,

input logic [3:0] k,

output logic [15:0] twiddle);

case(k)

4'b0000: twiddle = 16'h7fff;

4'b0001: twiddle = 16'h7d89;

4'b0010: twiddle = 16'h7641;

4'b0011: twiddle = 16'h6a6d;

4'b0100: twiddle = 16'h5a82;

4'b0101: twiddle = 16'h471c;

4'b0110: twiddle = 16'h30fb;

4'b0111: twiddle = 16'h18f9;

4'b1001: twiddle = 16'he707;

4'b1010: twiddle = 16'hcf05;

4'b1011: twiddle = 16'hb8e4;

4'b1100: twiddle = 16'ha57e;

4'b1101: twiddle = 16'h9593;

4'b1110: twiddle = 16'h89bf;

4'b1111: twiddle = 16'h8277;

default: twiddle = 16'h1111;

endmodule: RealTwiddles

```

```

Table II of the Slade Paper

inputs:

outputs:

module ImagTwiddles (input logic clk,

input logic [3:0] k,

case(k)

4'b0000: twiddle = 16'h0000;

4'b0001: twiddle = 16'h1859;

4'b0010: twiddle = 16'h30fb;

4'b0011: twiddle = 16'h471c;

4'b0100: twiddle = 16'h5a82;

4'b0101: twiddle = 16'h6a6d;

4'b0110: twiddle = 16'h7641;

4'b0111: twiddle = 16'h7d89;

4'b1000: twiddle = 16'h7fff;

4'b1001: twiddle = 16'h7d89;

4'b1011: twiddle = 16'h6a6d;

4'b1100: twiddle = 16'h5a82;

4'b1101: twiddle = 16'h471c;

4'b1110: twiddle = 16'h30fb;

4'b1111: twiddle = 16'h1859;

default: twiddle = 16'h0000;

endmodule: ImagTwiddles

```

#### RAM Module

```

/*

Module for the RAM

inputs:

```

```

clk = system clock

we = write enable

adressA = address for the a data

addressB = address for the b data

aWriteData = a data to be written in

addressB = b data to be written in

output:

aReadData = a data that will be fed to BFU

bReadData = b data that will be fed to BFU

module RAM(input logic clk, we,

input logic [4:0] addressB, addressA,

input logic [15:0] aWriteData, bWriteData,

output logic [15:0] aReadData, bReadData);

always ff@(posedge clk) begin

if (we) begin

mem array [addressB] <= aWriteData;</pre>

mem array [addressA] <= bWriteData;</pre>

aReadData <= aWriteData;</pre>

bReadData <= bWriteData;</pre>

aReadData <= mem array[addressB];</pre>

bReadData <= mem array[addressA];</pre>

```

## AGU FSM Next State Logic

|    | Source State | Destination State |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

|----|--------------|-------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1  | CLEAR        | READ              |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| 2  | DONE         | DONE              |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| 3  | LOAD         | LOAD              | $\label{lem:counter_0} \label{lem:counter_0} $$ ($counter[0]).($counter[2]).($counter[3]).($counter[4]) + ($counter[0]).($counter[1]).($counter[2]).($counter[2]).($counter[3]).($counter[3]).($counter[3]).($counter[3]).($counter[3]).($counter[3]).($counter[3]).($counter[3]).($counter[3]).($counter[3]).($counter[3]).($counter[3]).($counter[3]).($counter[3]).($counter[3]).($counter[3]).($counter[3]).($counter[3]).($counter[3]).($counter[3]).($counter[3]).($counter[3]).($counter[3]).($counter[3]).($counter[3]).($counter[3]).($counter[3]).($counter[3]).($counter[3]).($counter[3]).($counter[3]).($counter[3]).($counter[3]).($counter[3]).($counter[3]).($counter[3]).($counter[3]).($counter[3]).($counter[3]).($counter[3]).($counter[3]).($counter[3]).($counter[3]).($counter[3]).($counter[3]).($counter[3]).($counter[3]).($counter[3]).($counter[3]).($counter[3]).($counter[3]).($counter[3]).($counter[3]).($counter[3]).($counter[3]).($counter[3]).($counter[3]).($counter[3]).($counter[3]).($counter[3]).($counter[3]).($counter[3]).($counter[3]).($counter[3]).($counter[3]).($counter[3]).($counter[3]).($counter[3]).($counter[3]).($counter[3]).($counter[3]).($counter[3]).($counter[3]).($counter[3]).($counter[3]).($counter[3]).($counter[3]).($counter[3]).($counter[3]).($counter[3]).($counter[3]).($counter[3]).($counter[3]).($counter[3]).($counter[3]).($counter[3]).($counter[3]).($counter[3]).($counter[3]).($counter[3]).($counter[3]).($counter[3]).($counter[3]).($counter[3]).($counter[3]).($counter[3]).($counter[3]).($counter[3]).($counter[3]).($counter[3]).($counter[3]).($counter[3]).($counter[3]).($counter[3]).($counter[3]).($counter[3]).($counter[3]).($counter[3]).($counter[3]).($counter[3]).($counter[3]).($counter[3]).($counter[3]).($counter[3]).($counter[3]).($counter[3]).($counter[3]).($counter[3]).($counter[3]).($counter[3]).($counter[3]).($counter[3]).($counter[3]).($counter[3]).($counter[3]).($counter[3]).($counter[3]).($counter[3]).($counter[3]).($counter[3]).($counter[3]).($counter[3]).($counter[3]).($counter[3]).($count$ |

| 4  | LOAD         | WAIT              | $\label{lem:counter_0} $$ (!counter[0]).(!counter[2]).(!counter[3]).(counter[4]).(counter[5]) + (!counter[0]).(!counter[1]).(!counter[2]).(counter[2]).(counter[4]).(counter[5]) + (!counter[6]).(!counter[6]).(!counter[6]).(!counter[6]).(!counter[6]).(!counter[6]).(!counter[6]).(!counter[6]).(!counter[6]).(!counter[6]).(!counter[6]).(!counter[6]).(!counter[6]).(!counter[6]).(!counter[6]).(!counter[6]).(!counter[6]).(!counter[6]).(!counter[6]).(!counter[6]).(!counter[6]).(!counter[6]).(!counter[6]).(!counter[6]).(!counter[6]).(!counter[6]).(!counter[6]).(!counter[6]).(!counter[6]).(!counter[6]).(!counter[6]).(!counter[6]).(!counter[6]).(!counter[6]).(!counter[6]).(!counter[6]).(!counter[6]).(!counter[6]).(!counter[6]).(!counter[6]).(!counter[6]).(!counter[6]).(!counter[6]).(!counter[6]).(!counter[6]).(!counter[6]).(!counter[6]).(!counter[6]).(!counter[6]).(!counter[6]).(!counter[6]).(!counter[6]).(!counter[6]).(!counter[6]).(!counter[6]).(!counter[6]).(!counter[6]).(!counter[6]).(!counter[6]).(!counter[6]).(!counter[6]).(!counter[6]).(!counter[6]).(!counter[6]).(!counter[6]).(!counter[6]).(!counter[6]).(!counter[6]).(!counter[6]).(!counter[6]).(!counter[6]).(!counter[6]).(!counter[6]).(!counter[6]).(!counter[6]).(!counter[6]).(!counter[6]).(!counter[6]).(!counter[6]).(!counter[6]).(!counter[6]).(!counter[6]).(!counter[6]).(!counter[6]).(!counter[6]).(!counter[6]).(!counter[6]).(!counter[6]).(!counter[6]).(!counter[6]).(!counter[6]).(!counter[6]).(!counter[6]).(!counter[6]).(!counter[6]).(!counter[6]).(!counter[6]).(!counter[6]).(!counter[6]).(!counter[6]).(!counter[6]).(!counter[6]).(!counter[6]).(!counter[6]).(!counter[6]).(!counter[6]).(!counter[6]).(!counter[6]).(!counter[6]).(!counter[6]).(!counter[6]).(!counter[6]).(!counter[6]).(!counter[6]).(!counter[6]).(!counter[6]).(!counter[6]).(!counter[6]).(!counter[6]).(!counter[6]).(!counter[6]).(!counter[6]).(!counter[6]).(!counter[6]).(!counter[6]).(!counter[6]).(!counter[6]).(!counter[6]).(!counter[6]).(!counter[6]).(!counter[6]).(!counter[6]).(!counter[6]).(!co$ |

| 5  | READ         | WRITE             |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| 6  | WAIT         | LOAD              | (load).(!start)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| 7  | WAIT         | WAIT              | (!load).(!start)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

| 8  | WAIT         | CLEAR             | (start)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

| 9  | WRITE        | READ              | (!always2)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

| 10 | WRITE        | DONE              | (always2)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

# Top-Level Module Next State Logic

|   | Source State | Destination State |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

|---|--------------|-------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1 | CALCULATING  | READING           | (!ittCalc[2]).(!ittCalc[3]).(!ittCalc[4]).(!ittCalc[5]).(!ittCalc[6]).(!ittCalc[7]) + (!ittCalc[2]).(!ittCalc[3]).(!ittCalc[4]).(!ittCalc[5]).(!ittCalc[6]).(!ittCalc[6]).(!ittCalc[6]).(!ittCalc[6]).(!ittCalc[6]).(!ittCalc[6]).(!ittCalc[6]).(!ittCalc[6]).(!ittCalc[6]).(!ittCalc[6]).(!ittCalc[6]).(!ittCalc[6]).(!ittCalc[6]).(!ittCalc[6]).(!ittCalc[6]).(!ittCalc[6]).(!ittCalc[6]).(!ittCalc[6]).(!ittCalc[6]).(!ittCalc[6]).(!ittCalc[6]).(!ittCalc[6]).(!ittCalc[6]).(!ittCalc[6]).(!ittCalc[6]).(!ittCalc[6]).(!ittCalc[6]).(!ittCalc[6]).(!ittCalc[6]).(!ittCalc[6]).(!ittCalc[6]).(!ittCalc[6]).(!ittCalc[6]).(!ittCalc[6]).(!ittCalc[6]).(!ittCalc[6]).(!ittCalc[6]).(!ittCalc[6]).(!ittCalc[6]).(!ittCalc[6]).(!ittCalc[6]).(!ittCalc[6]).(!ittCalc[6]).(!ittCalc[6]).(!ittCalc[6]).(!ittCalc[6]).(!ittCalc[6]).(!ittCalc[6]).(!ittCalc[6]).(!ittCalc[6]).(!ittCalc[6]).(!ittCalc[6]).(!ittCalc[6]).(!ittCalc[6]).(!ittCalc[6]).(!ittCalc[6]).(!ittCalc[6]).(!ittCalc[6]).(!ittCalc[6]).(!ittCalc[6]).(!ittCalc[6]).(!ittCalc[6]).(!ittCalc[6]).(!ittCalc[6]).(!ittCalc[6]).(!ittCalc[6]).(!ittCalc[6]).(!ittCalc[6]).(!ittCalc[6]).(!ittCalc[6]).(!ittCalc[6]).(!ittCalc[6]).(!ittCalc[6]).(!ittCalc[6]).(!ittCalc[6]).(!ittCalc[6]).(!ittCalc[6]).(!ittCalc[6]).(!ittCalc[6]).(!ittCalc[6]).(!ittCalc[6]).(!ittCalc[6]).(!ittCalc[6]).(!ittCalc[6]).(!ittCalc[6]).(!ittCalc[6]).(!ittCalc[6]).(!ittCalc[6]).(!ittCalc[6]).(!ittCalc[6]).(!ittCalc[6]).(!ittCalc[6]).(!ittCalc[6]).(!ittCalc[6]).(!ittCalc[6]).(!ittCalc[6]).(!ittCalc[6]).(!ittCalc[6]).(!ittCalc[6]).(!ittCalc[6]).(!ittCalc[6]).(!ittCalc[6]).(!ittCalc[6]).(!ittCalc[6]).(!ittCalc[6]).(!ittCalc[6]).(!ittCalc[6]).(!ittCalc[6]).(!ittCalc[6]).(!ittCalc[6]).(!ittCalc[6]).(!ittCalc[6]).(!ittCalc[6]).(!ittCalc[6]).(!ittCalc[6]).(!ittCalc[6]).(!ittCalc[6]).(!ittCalc[6]).(!ittCalc[6]).(!ittCalc[6]).(!ittCalc[6]).(!ittCalc[6]).(!ittCalc[6]).(!ittCalc[6]).(!ittCalc[6]).(!ittCalc[6]).(!ittCalc[6]).(!ittCalc[6]).(!ittCalc[6]).(!ittCalc[6]).(!ittCalc[6]).(!ittCalc[6]).(!ittCalc[6]).(!ittCalc[6]).(!ittCalc[6]).(!ittCalc[6] |

| 2 | CALCULATING  | CALCULATING       | (!ittCalc[2]).(!ittCalc[3]).(!ittCalc[4]).(!ittCalc[5]).(!ittCalc[6]) + (!ittCalc[2]).(!ittCalc[3]).(!ittCalc[4]).(!ittCalc[5]).(!ittCalc[6]).(!ittCalc[6]).(!ittCalc[6]).(!ittCalc[6]).(!ittCalc[6]).(!ittCalc[6]).(!ittCalc[6]).(!ittCalc[6]).(!ittCalc[6]).(!ittCalc[6]).(!ittCalc[6]).(!ittCalc[6]).(!ittCalc[6]).(!ittCalc[6]).(!ittCalc[6]).(!ittCalc[6]).(!ittCalc[6]).(!ittCalc[6]).(!ittCalc[6]).(!ittCalc[6]).(!ittCalc[6]).(!ittCalc[6]).(!ittCalc[6]).(!ittCalc[6]).(!ittCalc[6]).(!ittCalc[6]).(!ittCalc[6]).(!ittCalc[6]).(!ittCalc[6]).(!ittCalc[6]).(!ittCalc[6]).(!ittCalc[6]).(!ittCalc[6]).(!ittCalc[6]).(!ittCalc[6]).(!ittCalc[6]).(!ittCalc[6]).(!ittCalc[6]).(!ittCalc[6]).(!ittCalc[6]).(!ittCalc[6]).(!ittCalc[6]).(!ittCalc[6]).(!ittCalc[6]).(!ittCalc[6]).(!ittCalc[6]).(!ittCalc[6]).(!ittCalc[6]).(!ittCalc[6]).(!ittCalc[6]).(!ittCalc[6]).(!ittCalc[6]).(!ittCalc[6]).(!ittCalc[6]).(!ittCalc[6]).(!ittCalc[6]).(!ittCalc[6]).(!ittCalc[6]).(!ittCalc[6]).(!ittCalc[6]).(!ittCalc[6]).(!ittCalc[6]).(!ittCalc[6]).(!ittCalc[6]).(!ittCalc[6]).(!ittCalc[6]).(!ittCalc[6]).(!ittCalc[6]).(!ittCalc[6]).(!ittCalc[6]).(!ittCalc[6]).(!ittCalc[6]).(!ittCalc[6]).(!ittCalc[6]).(!ittCalc[6]).(!ittCalc[6]).(!ittCalc[6]).(!ittCalc[6]).(!ittCalc[6]).(!ittCalc[6]).(!ittCalc[6]).(!ittCalc[6]).(!ittCalc[6]).(!ittCalc[6]).(!ittCalc[6]).(!ittCalc[6]).(!ittCalc[6]).(!ittCalc[6]).(!ittCalc[6]).(!ittCalc[6]).(!ittCalc[6]).(!ittCalc[6]).(!ittCalc[6]).(!ittCalc[6]).(!ittCalc[6]).(!ittCalc[6]).(!ittCalc[6]).(!ittCalc[6]).(!ittCalc[6]).(!ittCalc[6]).(!ittCalc[6]).(!ittCalc[6]).(!ittCalc[6]).(!ittCalc[6]).(!ittCalc[6]).(!ittCalc[6]).(!ittCalc[6]).(!ittCalc[6]).(!ittCalc[6]).(!ittCalc[6]).(!ittCalc[6]).(!ittCalc[6]).(!ittCalc[6]).(!ittCalc[6]).(!ittCalc[6]).(!ittCalc[6]).(!ittCalc[6]).(!ittCalc[6]).(!ittCalc[6]).(!ittCalc[6]).(!ittCalc[6]).(!ittCalc[6]).(!ittCalc[6]).(!ittCalc[6]).(!ittCalc[6]).(!ittCalc[6]).(!ittCalc[6]).(!ittCalc[6]).(!ittCalc[6]).(!ittCalc[6]).(!ittCalc[6]).(!ittCalc[6]).(!ittCalc[6]).(!ittCalc[6]).(!ittCalc[6]).(!ittCalc[6]).(!ittCalc[6] |

| 3 | COLLECTING   | COLLECTING        | (spiload)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

| 4 | COLLECTING   | LOADING           | (!spiload)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |